在即将于12月7日至11日在旧金山举行的国际电子器件会议(IEDM)上,Geoffrey Yeap将作题为“5nm CMOS Production Technology Platform Featuring Full-Fledged EUV and High-Mobility Channel FinFETs with Densest 0.021µm2 SRAM Cells for Mobile SoC and High-Performance Computing Applications”的演讲报告。

过去一段时间以来,有关5纳米(N5)工艺的详细信息已逐步披露,最近一次是在4月在圣克拉拉举行的技术研讨会和上个月的台积电Open Innovation Platform Innovation Forum上。这两个会议所披露的信息,总结如下(不分先后顺序):

- 面向高性能计算和移动客户

- 于2019年3月开始风险量产;在2020年第2季度实现了大批量生产(在台南Gigafab18,第1阶段设备安装已于19年3月完成)

- 一年后将推出N5P(performance)版本,与N5相比,在恒定功率下性能提高+7%,在恒定性能下功耗降低约15%

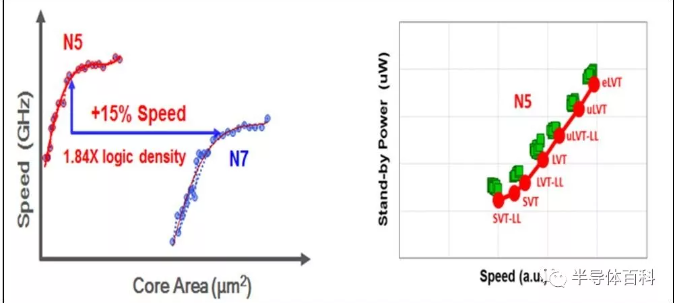

- 与7nm相比,逻辑密度提高到1.8倍,SRAM面积缩为0.75倍,Analog区域面积缩到0.85倍。

- 同功耗下比7nm快15%,或者在相同速度下功耗降低30%。

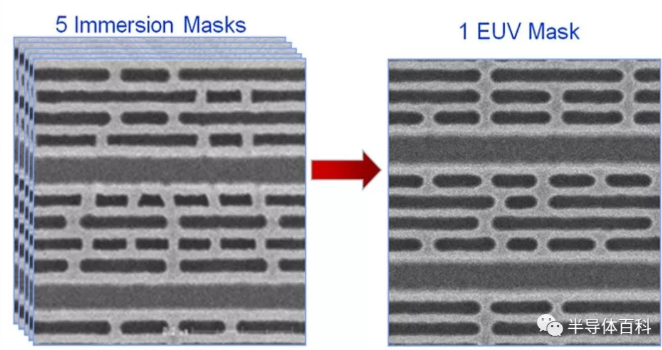

- 引入了EUV

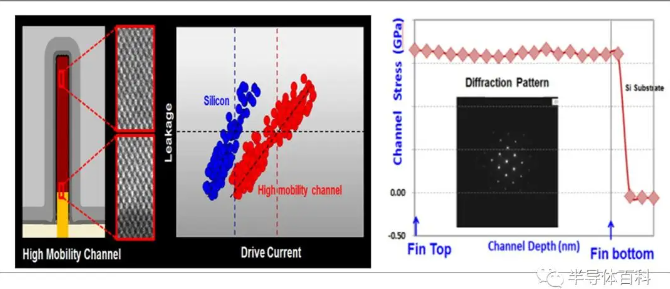

- 将有一个高迁移率沟道(Ge?)晶体管

- 低电阻接触(contact)和过孔(via)。

- 更多的器件选项,包括提供1.5V或1.2V的I / O晶体管,以及extreme LVT器件,其速度比7纳米等效器件快25%。

- HPC标准单元中Viapillars和优化的金属化工艺提供10%的性能提升

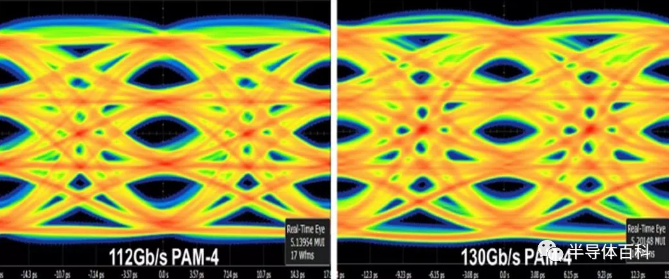

- 提供112Gbps SerDes的传输性能。

- 超高密度MIM电容器结构,具有2倍ff /µm2和2倍的插入密度,可将速度提高4%

- 新型低介电常数材料

- 金属的等离子蚀刻(RIE)工艺,在节距小于30nm时取代铜的大马士革铜工艺

- 石墨烯“cap”以降低铜互连电阻率

感谢SemiWiki的Tom Dillinger和BreakfastBytes的Paul McLellan的先前报道。

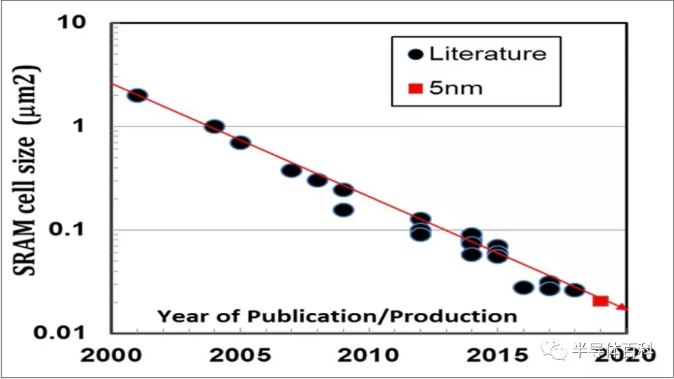

在IEDM新闻材料和会议摘要中,以上大部分内容都得到了重申。逻辑密度相比7nm更确切的数字是1.84倍,,并且在引入EUV光刻(图2)和高迁移率沟道FinFET(图3)后其5nm相比7nm有15%的速度增加或30%的功耗下降。此外,最多可提供7个Vt(图1)。该公司还强调其SRAM单元是有史以来最小的,为0.021µm2。

在测试电路中,PAM4 SerDes Transmitter模块展示了130Gb / s的速度和0.96pJ/ bit的能效。预计该技术将在2020年上半年通过高良率量产验证。

如果M1的节距为30nm,则需要SAQP或LE3,加上几张cut光罩,这里一张EUV光罩即可。假设金属节距是30nm,对图片进行量测可以得到,标准单元高度大概是〜175 nm(〜5.8单元高度),与7nm工艺相比,线性缩放为〜0.73。此外,我们可以看到EUV工艺图形更加清晰。

有评论认为这可能是Ge沟道的fin,但考虑到Ge和Si之间的晶格失配会产生位错,高达40%的Ge含量的SiGe沟道可能性较高。

上面显示的鳍片的高倍放大TEM晶格图像表明沟道方向是常规的<110>方向,但奇怪的是,右侧的衍射图像似乎是在<100>方向上拍摄的。

IEDM预告中没有提及5nm的相关工艺;新型的低k电介质不足为奇,但是铜的干法蚀刻(如果采用)据我所知将是首次。难道是原子层蚀刻(ALE)技术的发展应用?此外我们在文献中已经看到了石墨烯金属cap,这也是业界首次应用。

看起来将是一个令人兴奋的报告,但是您需要耐心等待。其论文编号是36.7,报告时间是12月11日(星期三)4:05pm,是该主题的最后一个报告,也可能是整个会议的最后一个报告!

本文由IC 字幕组 Jason Jin 翻译自semiconductor-digest,阅读原文请点坐下角。