单MOS管的寄生参数提取

在/home/IC/Documents/jingying/CUMEC_PDK/CUMEC013_PDK_V0p5_Release_20220615/CUMEC130_PDK_OA_V0p5_20220615目录下进行本次设计。

建立反相器版图cell,p管为p1p5_lvs_sct长宽为1um*6um,n管为n1p5_lvs_sct长宽为1um*2um。根据模拟版图画反相器的版图,参考:https://www.cnblogs.com/sasasatori/p/16041328.html,以及之前的博文:模拟版图实践。

在cumec PDK中版图过程中,有一些层目前还没有解释,例如VTNL和VTPL以及VPO层,我们先用smic18 PDK做下去。

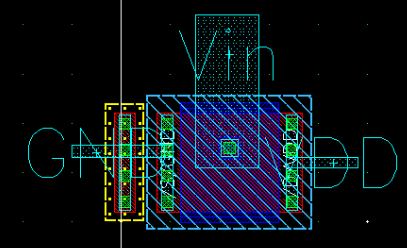

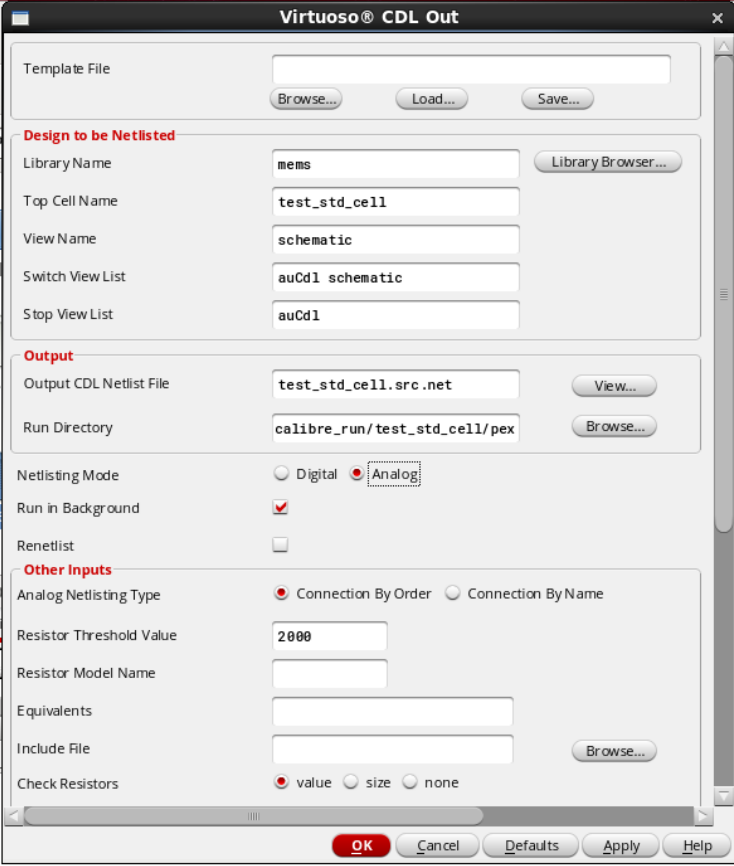

我们先做一个简单的单n管版图,在redhat虚拟机中的位置时mems/test_std_cell,注意要按Q键调出Edit Instance Properties页面,Parameter选项卡,Bodytie Tie这里选择Detached,然后将B极调出来。GND与B极用M1连接起来如下图所示。连接完成后按L键打标。之后做DRC,LVS。DRC很简单这里就不多说了,LVS要提前将原理图在CID窗口中以cdl格式以analog模式导出,文件的后缀一般写.src.net。在启动nmLVS界面后,Layout面板可以直接Export from layout viewer。运行完LVS后,可以进行PEX。

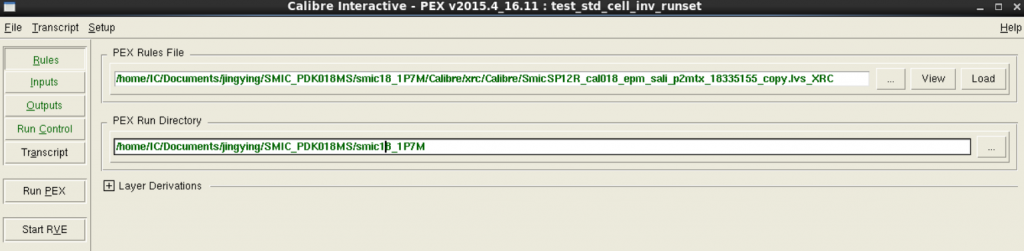

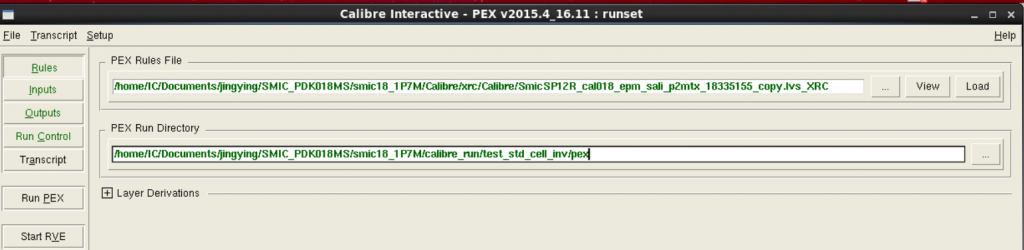

PEX的规则文件为/home/IC/Documents/jingying/SMIC_PDK018MS/smic18_1P7M/Calibre/xrc/Calibre/SmicSP12R_cal018_epm_sali_p2mtx_18335155_copy.lvs_XRC。

.src.net文件为CDL格式,导出方法为CIW窗口File->Export->CDL,设置细节如下:

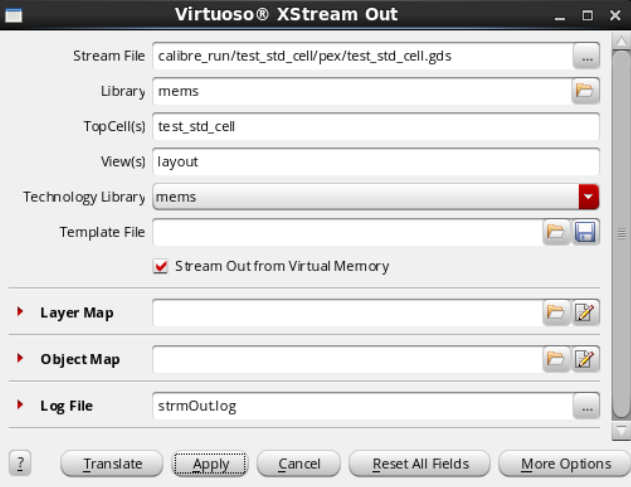

除此之外有时候还需要导出gds文件,可以在CIW窗口File->Export->Stream实施:

PEX Run Directory选择一个干净的目录,将上面的.src.net放进去。

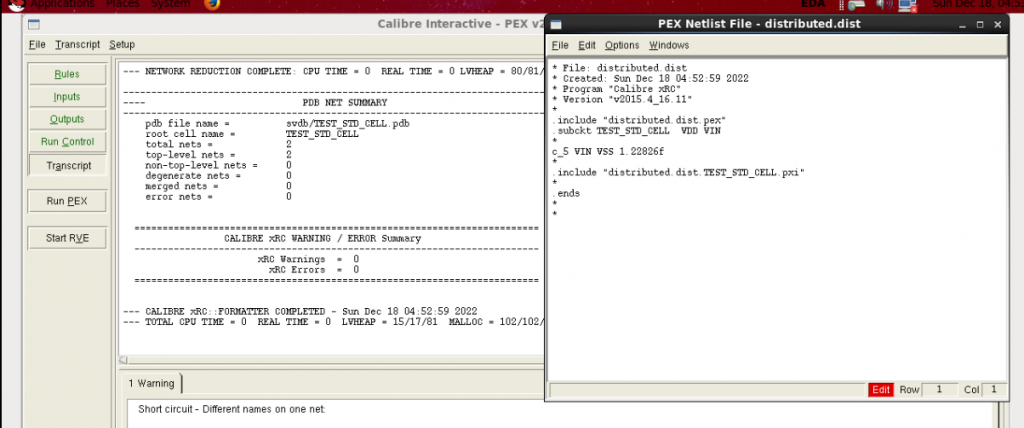

之后启动PEX即可。运行结束后得到下面这个界面,代表PEX完成。

— OUTPUT PARASITIC MODEL FILE NAME distributed.dist.pex

— PROCESSING PARASITIC MODELS

— OUTPUT PARASITIC MODEL INSTANCE FILE NAME distributed.dist.TEST_STD_CELL.pxi

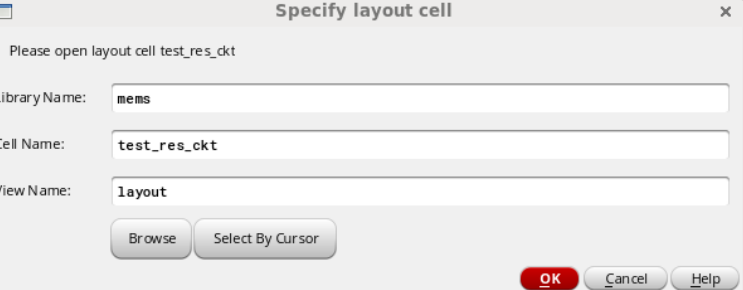

设置好后会出现一个确认框

反相器的寄生参数提取

接下来创建名为test_std_cell_inv的cell。经过上面的探索,我们现在可以步子迈得大一些。首先建立空白目录*/calibre_run/test_std_cell_inv/pex,在CIW导出CDL格式的src.net文件到该目录下。打开Calibre PEX,在Rules页面填入以下内容

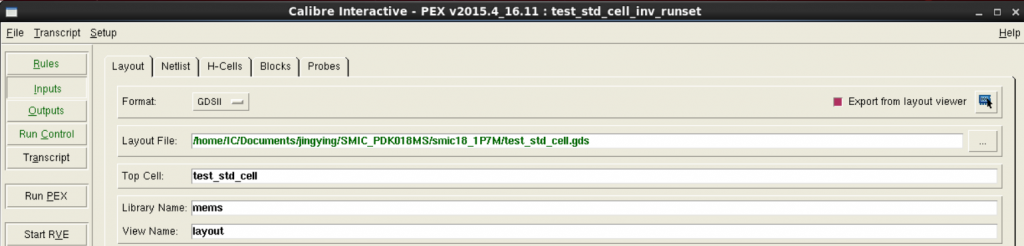

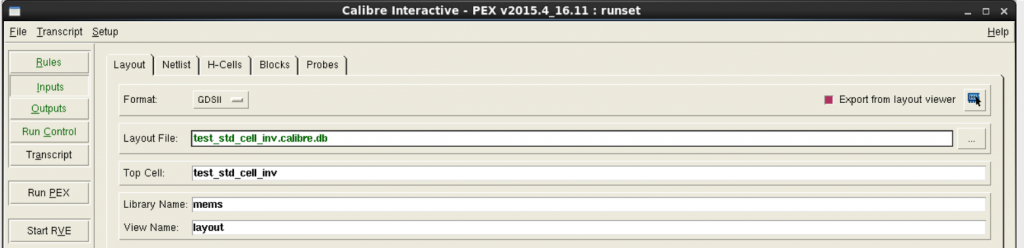

打开Inputs页面,在Layout选项卡处搞出下图这样的东西:

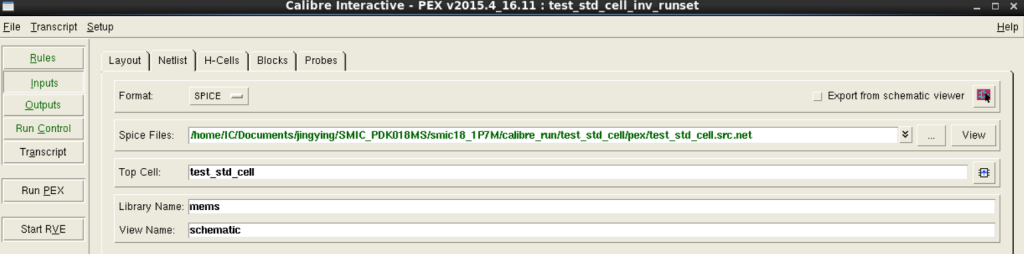

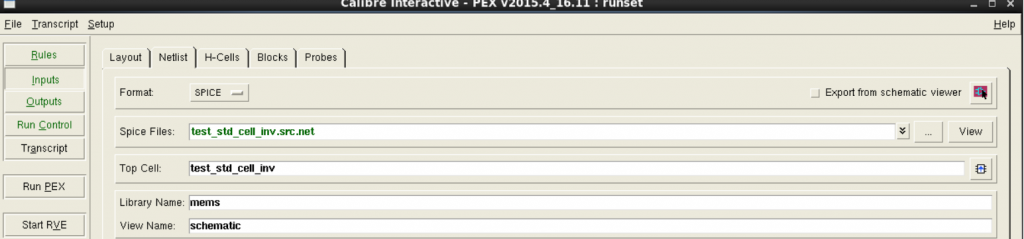

切换到Netlists选项卡,设置成下图这样:

接下来即可进行Run PEX的操作,操作完成后,可以把操作过程存储为Runset文件,我们这次的操作过程的Runset文件如下:

*pexRulesFile: /home/IC/Documents/jingying/SMIC_PDK018MS/smic18_1P7M/Calibre/xrc/Calibre/SmicSP12R_cal018_epm_sali_p2mtx_18335155_copy.lvs_XRC

*pexRulesFileLastLoad: 1671325983

*pexRunDir: /home/IC/Documents/jingying/SMIC_PDK018MS/smic18_1P7M/calibre_run/test_std_cell_inv/pex

*pexLayoutPaths: test_std_cell_inv.calibre.db

*pexLayoutPrimary: test_std_cell_inv

*pexLayoutLibrary: mems

*pexLayoutView: layout

*pexLayoutGetFromViewer: 1

*pexSourcePath: test_std_cell_inv.src.net

*pexSourcePrimary: test_std_cell_inv

*pexSourceLibrary: mems

*pexSourceView: schematic

*pexPexTopLevelExcludeNetsValue: VSS

*pexPexGroundName: 1

*pexPexGroundNameValue: VSS

*pexResistanceParameters: 1

*pexResistanceParametersValue: {gppoly TC1 0.00292 TC2 -2.3e-08} {metal1 TC1 0.00349 TC2 6.93e-07} {metal2 TC1 0.0036 TC2 7.6e-07} {metal3 TC1 0.0036 TC2 7.6e-07} {metal4 TC1 0.0036 TC2 7.6e-07} {metal5a TC1 0.0036 TC2 7.6e-07} {metal6 TC1 0.00389 TC2 1.01e-06} {gtpoly TC1 0.00292 TC2 -2.3e-08}

*pexPowerNames: VDD SAVDD? ?VDD? ?VCC? ?vcc? ?vdd?

*pexGroundNames: VSS SAVSS? ?GND? ?VSS? ?vss? ?gnd?

*pexReportFile: test_std_cell_inv.lvs.report

*pexPexNetlistFile: test_std_cell_inv.pex.netlist

*pexPexNetlistFormat: HSPICE

*pexPexNetlistNameSource: LAYOUTNAMES

*pexPexReport: 1

*pexPexReportFile: test_std_cell_inv.pex.report

*pexPexPinNameSepValue:

*pexPexSeparatorValue:

*pexReportOptions: A B C D S

*pexLayoutDeviceFilterOptions: AB RC RE RG

*pexSourceDeviceFilterOptions: AB RC RE RG

*pexRecognizeGates: NONE

*cmnVConnectColon: 1

*cmnUseCBforRVE: 0

*cmnRunHier: 2

*cmnSlaveHosts: {use {}} {hostName {}} {cpuCount {}} {a32a64 {}} {rsh {}} {maxMem {}} {workingDir {}} {layerDir {}} {mgcLibPath {}} {launchName {}}

*cmnLSFSlaveTbl: {use 1} {totalCpus 1} {minCpus 1} {architecture {{}}} {minMemory {{}}} {resourceOptions {{}}} {submitOptions {{}}}

*cmnGridSlaveTbl: {use 1} {totalCpus 1} {minCpus 1} {architecture {{}}} {minMemory {{}}} {resourceOptions {{}}} {submitOptions {{}}}

*cmnFDILayoutLibrary: mems

*cmnFDILayoutView: layout

*cmnFDIDEFLayoutPath: test_std_cell_inv.def

*cmnTraceProperties: {1 { MN(N18E2R) "L" "L" 5 5}} {1 { MN(N18E2R) "W" "W" 5 5}} {1 { MN(NZ18E2R) "L" "L" 5 5}} {1 { MN(NZ18E2R) "W" "W" 5 5}} {1 { MP(P18E2R) "L" "L" 5 5}} {1 { MP(P18E2R) "W" "W" 5 5}} {1 { MN(N33E2R) "L" "L" 5 5}} {1 { MN(N33E2R) "W" "W" 5 5}} {1 { MP(P33E2R) "L" "L" 5 5}} {1 { MP(P33E2R) "W" "W" 5 5}} {1 { MN(N50E2R) "L" "L" 5 5}} {1 { MN(N50E2R) "W" "W" 5 5}} {1 { MP(P50E2R) "L" "L" 5 5}} {1 { MP(P50E2R) "W" "W" 5 5}} {1 { MN(NZ50E2R) "L" "L" 5 5}} {1 { MN(NZ50E2R) "W" "W" 5 5}} {1 { MN(N155E2R) "L" "L" 5 5}} {1 { MN(N155E2R) "W" "W" 5 5}} {1 { MN(NZ155E2R) "L" "L" 5 5}} {1 { MN(NZ155E2R) "W" "W" 5 5}} {1 { MP(P155E2R) "L" "L" 5 5}} {1 { MP(P155E2R) "W" "W" 5 5}} {1 { MN(N18D) "L" "L" 5 5}} {1 { MN(N18D) "W" "W" 5 5}} {1 { MN(N18H) "L" "L" 5 5}} {1 { MN(N18H) "W" "W" 5 5}} {1 { MN(NSG) "L" "L" 5 5}} {1 { MN(NSG) "W" "W" 5 5}} {1 { MN(NCG) "L" "L" 5 5}} {1 { MN(NCG) "W" "W" 5 5}} {1 { pvar18e2r_ckt "WR" "WR" 5 5}} {1 { pvar18e2r_ckt "LR" "LR" 5 5}} {1 { pvar18e2r_ckt "NF" "NF" 0 0}} {1 { Q(PNP18A4E2R) "A" "A" 5 5}} {1 { Q(PNP18A25E2R) "A" "A" 5 5}} {1 { Q(PNP18A100E2R) "A" "A" 5 5}} {1 { Q(PNP33A4E2R) "A" "A" 5 5}} {1 { Q(PNP33A25E2R) "A" "A" 5 5}} {1 { Q(PNP33A100E2R) "A" "A" 5 5}} {1 { D(PDIO18E2R) "A" "A" 5 5}} {1 { D(PDIO33E2R) "A" "A" 5 5}} {1 { D(PDIO50E2R) "A" "A" 5 5}} {1 { D(PDIO155E2R) "A" "A" 5 5}} {1 { D(NDIO18E2R) "A" "A" 5 5}} {1 { D(NDIO33E2R) "A" "A" 5 5}} {1 { D(NDIO50E2R) "A" "A" 5 5}} {1 { D(NDIO155E2R) "A" "A" 5 5}} {1 { D(NZDIO50E2R) "A" "A" 5 5}} {1 { D(NZDIO155E2R) "A" "A" 5 5}} {1 { D(NWDIOE2R) "A" "A" 5 5}} {1 { D(DNWDIOE2R) "A" "A" 5 5}} {1 { C(CGTTOW) "C" "C" 5 5}} {1 { pipe2r_ckt "C" "C" 5 5}} {1 { mime2r_ckt "LR" "LR" 5 5}} {1 { mime2r_ckt "WR" "WR" 5 5}} {1 { R(RPGT) "R" "R" 5 5}} {1 { R(RNGTSAB) "R" "R" 5 5}} {1 { R(RPGTSAB) "R" "R" 5 5}} {1 { R(RNCGSAB) "R" "R" 5 5}} {1 { rndif_ckt "W" "W" 5 5}} {1 { rndif_ckt "L" "L" 5 5}} {1 { rpdif_ckt "W" "W" 5 5}} {1 { rpdif_ckt "L" "L" 5 5}} {1 { rnpo_ckt "W" "W" 5 5}} {1 { rnpo_ckt "L" "L" 5 5}} {1 { rnpo_3t_ckt "W" "W" 5 5}} {1 { rnpo_3t_ckt "L" "L" 5 5}} {1 { rppo_ckt "W" "W" 5 5}} {1 { rppo_ckt "L" "L" 5 5}} {1 { rppo_3t_ckt "W" "W" 5 5}} {1 { rppo_3t_ckt "L" "L" 5 5}} {1 { rnwaa_ckt "W" "W" 5 5}} {1 { rnwaa_ckt "L" "L" 5 5}} {1 { rnwsti_ckt "W" "W" 5 5}} {1 { rnwsti_ckt "L" "L" 5 5}} {1 { rndifsab_ckt "W" "W" 5 5}} {1 { rndifsab_ckt "L" "L" 5 5}} {1 { rpdifsab_ckt "W" "W" 5 5}} {1 { rpdifsab_ckt "L" "L" 5 5}} {1 { rnposab_ckt "W" "W" 5 5}} {1 { rnposab_ckt "L" "L" 5 5}} {1 { rnposab_3t_ckt "W" "W" 5 5}} {1 { rnposab_3t_ckt "L" "L" 5 5}} {1 { rpposab_ckt "W" "W" 5 5}} {1 { rpposab_ckt "L" "L" 5 5}} {1 { rpposab_3t_ckt "W" "W" 5 5}} {1 { rpposab_3t_ckt "L" "L" 5 5}} {1 { rhrpo_ckt "W" "W" 5 5}} {1 { rhrpo_ckt "L" "L" 5 5}} {1 { rhrpo_3t_ckt "W" "W" 5 5}} {1 { rhrpo_3t_ckt "L" "L" 5 5}} {1 { rtimsabe2r_ckt "W" "W" 5 5}} {1 { rtimsabe2r_ckt "L" "L" 5 5}} {1 { R(RM1) "R" "R" 5 5}} {1 { R(RM2) "R" "R" 5 5}} {1 { R(RM3) "R" "R" 5 5}} {1 { R(RM4) "R" "R" 5 5}} {1 { R(RM5) "R" "R" 5 5}} {1 { R(RM6) "R" "R" 5 5}}反相器时序库建模

Siliconsmart要登场了。需要lib库模板,仿真模型,以及电路网表。本节在eetop上一位前辈的帖子改版而来。

操作命令如下:

1. extrat all files to a directory

2. execute siliconsmart at the directory

3. in siliconsmart> promt, enter the below lines one by one

4. the new lib is created at my_library/models dir

cmd:

create my_library

cp configure.tcl my_library/config/

set_location my_library

import -liberty orig/lib/netlist.lib -netlist_dir orig/netlists -ext .cdl -overwrite -use_default_slews

configure -timing -power all

characterize all

model -create_new_model -file my_library/models/netlist.lib all -library_type typtcl文件如下:

# See SiliconSmart User Guide Appendix B for a complete list of parameters and definitions

#################################

# OPERATING CONDITIONS DEFINITION

#################################

#

# Create one or more operation conditions here. Example:

#

create_operating_condition tt_3p3v_25c

set_opc_process tt_3p3v_25c {

{.lib "/home/master/Work/smic18inv/orig/models/ms018_lcos_v0p5_rev0.lib" tt}

}

add_opc_supplies tt_3p3v_25c VDD 3.3

add_opc_grounds tt_3p3v_25c GND 0.0

set_opc_temperature tt_3p3v_25c 25

#

#################################

# GLOBAL CONFIGURATION PARAMETERS

#################################

define_parameters default {

# List of operating conditions as defined by create_operation_condition

set active_pvts { tt_3p3v_25c }

# If using IBIS, one operating condition must be specified in ibis_typ_pvt

# set ibis_typ_pvt tt_3p3v_25c

# FINESIM

# set simulator finesim

# set simulator_cmd {finesim_spice -w <input_deck> -o <listing_file> >&/dev/null}

# FINESIM EMBEDDED

# set simulator finesim_embedded

# HSPICE

set simulator hspice

set simulator_cmd {hspice <input_deck> -o <listing_file>}

# HSPICE (client/server mode)

# set simulator hspice_cs

# set simulator_cmd {hspice -CC <input_deck> -port <port_num> -o <listing_file>}

# SPECTRE

# set simulator spectre6

# set simulator_cmd {spectremdl -tab -batch <mdl_file> -design <input_deck> <listing_file> >&/dev/null}

# ELDO

# set simulator eldo

# set simulator_cmd {eldo -compat -i <input_deck> > <listing_file> >&/dev/null}

# MSIM

# set simulator msim

# (csh)

# set simulator_cmd {msim -hsp -i <input_deck> -o <listing_file> >&/dev/null}

# (sh)

# set simulator_cmd {msim -hsp -i <input_deck> -o <listing_file> 2>/dev/null}

# Default simulator options for Finesim, Hspice, Spectre, Msim, and Eldo

set simulator_options {

"common,finesim: finesim_mode=spicehd finesim_method=gear finesim_speed=0 finesim_dvmax=0.1"

"common,hspice: probe=1 runlvl=5 numdgt=7 measdgt=7 acct=1 nopage"

"common,spectre6: compression=yes step=10ps maxstep=1ns relref=allglobal"

"common,spectre6: method=trap lteratio=4 gmin=1e-18 autostop=0 save=none"

"common,msim: probe=1 accurate=1"

"common,eldo: gmindc=1n gmin=1p itl1=500 ingold=1 numdgt=4 measout=0 cptime=18000 relvar=0.01"

"op,eldo: dv=0.5 method=gear"

"tran,eldo: brief=0 relvar=0.001"

"optimize,eldo: lvltim=3 relvar=0.001"

"power,eldo: method=gear"

}

# Constraint settings:

# independent/dependent/dependent-setup/dependent-hold

set constraint_mode dependent

set smc_constraint_style relative-degradation

set smc_degrade 0.1

set path_constraint_mode off

# Simulation resolution

set time_res_high 1e-12

set time_res_low 100e-12

set nochange_variance [expr $time_res_high * 4.0]

set nochange_threshold 0.1

# Controls which supplies are measured for power consumption

set power_meas_supplies { VDD }

# list of ground supplies used (required for Functional Recognition)

set power_meas_grounds { GND }

set power_stabilization_threshold 0.05

set power_stabilization_threshold_absolute 1e-12

set model_negative_constraints true

set model_negative_delays true

set model_significant_digits 4

set model_ecsm_cin false

set liberty_cap_unit "1pf"

set Liberty_time_unit "1ns"

set liberty_increasing_delay_with_load off

set liberty_increasing_delay_with_slew off

set liberty_flavor "2008.09"

set liberty_max_capacitance 0

set liberty_max_transition 0

set liberty_leakage_power_unit "1mW"

set model_mpw_attribute false

# specifies which multi-rail format to be used in Liberty model; none, v1, or v2.

set liberty_multi_rail_format none

# LOAD SHARE PARAMETERS

# job_scheduler: 'lsf' (Platform), 'grid' (SunGrid), or 'standalone' (local machine)

set job_scheduler standalone

set run_list_maxsize 1

set normal_queue "lsf_queue_name"

set scheduler_poll_time 10

}

############################

# DEFAULT PINTYPE PARAMETERS

############################

pintype default {

set logic_high_name VDD

set logic_high_threshold 0.7

# set logic_high_name vout

# set logic_high_threshold 0.7

set logic_low_name GND

set logic_low_threshold 0.3

set prop_delay_level 0.5

set prop_delay_current 0.1

set driver_rise_time 10e-12

set driver_fall_time 10e-12

# Number of slew and load indices

# (when importing with -use_default_slews -use_default_loads)

set numsteps_slew 6

set numsteps_load 6

set constraint_numsteps_slew 3

# Operating load ranges

set smallest_load 1e-15

set largest_load 5.763e-13

# Operating slew ranges

set smallest_slew 20e-12

set largest_slew 3e-9

set max_tout 1.0e-9

# Automatically determine largest_load based on max_tout; off or on

set autorange_load off

# Noise of points in for noise height

set numsteps_height 8

# Input noise width.

set numsteps_width 5

# driver model: pwl, emulated, active, active-waveform, custom

set driver_mode pwl

# driver cell name (relevant only when driver_mode is "active")

set driver pwl

}

#####################################

# LIBERTY MODEL GENERATION PARAMETERS

#####################################

define_parameters liberty_model {

# Add Liberty header attributes here for use with "model -create_new_model"

set delay_model "table_lookup"

set default_fanout_load 1.0

set default_inout_pin_cap 9999

set default_input_pin_cap 9999

set default_output_pin_cap 0.0

set default_cell_leakage_power 0.0

set default_leakage_power_density 0.0

set slew_lower_threshold_pct_rise 30.0

set slew_lower_threshold_pct_fall 30.0

set slew_upper_threshold_pct_rise 70.0

set slew_upper_threshold_pct_fall 70.0

set input_threshold_pct_fall 50.0

set input_threshold_pct_rise 50.0

set output_threshold_pct_fall 50.0

set output_threshold_pct_rise 50.0

}

#######################

# VALIDATION PARAMETERS

#######################

lib库如下:

# See SiliconSmart User Guide Appendix B for a complete list of parameters and definitions

#################################

# OPERATING CONDITIONS DEFINITION

#################################

#

# Create one or more operation conditions here. Example:

#

create_operating_condition tt_3p3v_25c

set_opc_process tt_3p3v_25c {

{.lib "/home/master/Work/smic18inv/orig/models/ms018_lcos_v0p5_rev0.lib" tt}

}

add_opc_supplies tt_3p3v_25c VDD 3.3

add_opc_grounds tt_3p3v_25c GND 0.0

set_opc_temperature tt_3p3v_25c 25

#

#################################

# GLOBAL CONFIGURATION PARAMETERS

#################################

define_parameters default {

# List of operating conditions as defined by create_operation_condition

set active_pvts { tt_3p3v_25c }

# If using IBIS, one operating condition must be specified in ibis_typ_pvt

# set ibis_typ_pvt tt_3p3v_25c

# FINESIM

# set simulator finesim

# set simulator_cmd {finesim_spice -w <input_deck> -o <listing_file> >&/dev/null}

# FINESIM EMBEDDED

# set simulator finesim_embedded

# HSPICE

set simulator hspice

set simulator_cmd {hspice <input_deck> -o <listing_file>}

# HSPICE (client/server mode)

# set simulator hspice_cs

# set simulator_cmd {hspice -CC <input_deck> -port <port_num> -o <listing_file>}

# SPECTRE

# set simulator spectre6

# set simulator_cmd {spectremdl -tab -batch <mdl_file> -design <input_deck> <listing_file> >&/dev/null}

# ELDO

# set simulator eldo

# set simulator_cmd {eldo -compat -i <input_deck> > <listing_file> >&/dev/null}

# MSIM

# set simulator msim

# (csh)

# set simulator_cmd {msim -hsp -i <input_deck> -o <listing_file> >&/dev/null}

# (sh)

# set simulator_cmd {msim -hsp -i <input_deck> -o <listing_file> 2>/dev/null}

# Default simulator options for Finesim, Hspice, Spectre, Msim, and Eldo

set simulator_options {

"common,finesim: finesim_mode=spicehd finesim_method=gear finesim_speed=0 finesim_dvmax=0.1"

"common,hspice: probe=1 runlvl=5 numdgt=7 measdgt=7 acct=1 nopage"

"common,spectre6: compression=yes step=10ps maxstep=1ns relref=allglobal"

"common,spectre6: method=trap lteratio=4 gmin=1e-18 autostop=0 save=none"

"common,msim: probe=1 accurate=1"

"common,eldo: gmindc=1n gmin=1p itl1=500 ingold=1 numdgt=4 measout=0 cptime=18000 relvar=0.01"

"op,eldo: dv=0.5 method=gear"

"tran,eldo: brief=0 relvar=0.001"

"optimize,eldo: lvltim=3 relvar=0.001"

"power,eldo: method=gear"

}

# Constraint settings:

# independent/dependent/dependent-setup/dependent-hold

set constraint_mode dependent

set smc_constraint_style relative-degradation

set smc_degrade 0.1

set path_constraint_mode off

# Simulation resolution

set time_res_high 1e-12

set time_res_low 100e-12

set nochange_variance [expr $time_res_high * 4.0]

set nochange_threshold 0.1

# Controls which supplies are measured for power consumption

set power_meas_supplies { VDD }

# list of ground supplies used (required for Functional Recognition)

set power_meas_grounds { GND }

set power_stabilization_threshold 0.05

set power_stabilization_threshold_absolute 1e-12

set model_negative_constraints true

set model_negative_delays true

set model_significant_digits 4

set model_ecsm_cin false

set liberty_cap_unit "1pf"

set Liberty_time_unit "1ns"

set liberty_increasing_delay_with_load off

set liberty_increasing_delay_with_slew off

set liberty_flavor "2008.09"

set liberty_max_capacitance 0

set liberty_max_transition 0

set liberty_leakage_power_unit "1mW"

set model_mpw_attribute false

# specifies which multi-rail format to be used in Liberty model; none, v1, or v2.

set liberty_multi_rail_format none

# LOAD SHARE PARAMETERS

# job_scheduler: 'lsf' (Platform), 'grid' (SunGrid), or 'standalone' (local machine)

set job_scheduler standalone

set run_list_maxsize 1

set normal_queue "lsf_queue_name"

set scheduler_poll_time 10

}

############################

# DEFAULT PINTYPE PARAMETERS

############################

pintype default {

set logic_high_name VDD

set logic_high_threshold 0.7

# set logic_high_name vout

# set logic_high_threshold 0.7

set logic_low_name GND

set logic_low_threshold 0.3

set prop_delay_level 0.5

set prop_delay_current 0.1

set driver_rise_time 10e-12

set driver_fall_time 10e-12

# Number of slew and load indices

# (when importing with -use_default_slews -use_default_loads)

set numsteps_slew 6

set numsteps_load 6

set constraint_numsteps_slew 3

# Operating load ranges

set smallest_load 1e-15

set largest_load 5.763e-13

# Operating slew ranges

set smallest_slew 20e-12

set largest_slew 3e-9

set max_tout 1.0e-9

# Automatically determine largest_load based on max_tout; off or on

set autorange_load off

# Noise of points in for noise height

set numsteps_height 8

# Input noise width.

set numsteps_width 5

# driver model: pwl, emulated, active, active-waveform, custom

set driver_mode pwl

# driver cell name (relevant only when driver_mode is "active")

set driver pwl

}

#####################################

# LIBERTY MODEL GENERATION PARAMETERS

#####################################

define_parameters liberty_model {

# Add Liberty header attributes here for use with "model -create_new_model"

set delay_model "table_lookup"

set default_fanout_load 1.0

set default_inout_pin_cap 9999

set default_input_pin_cap 9999

set default_output_pin_cap 0.0

set default_cell_leakage_power 0.0

set default_leakage_power_density 0.0

set slew_lower_threshold_pct_rise 30.0

set slew_lower_threshold_pct_fall 30.0

set slew_upper_threshold_pct_rise 70.0

set slew_upper_threshold_pct_fall 70.0

set input_threshold_pct_fall 50.0

set input_threshold_pct_rise 50.0

set output_threshold_pct_fall 50.0

set output_threshold_pct_rise 50.0

}

#######################

# VALIDATION PARAMETERS

#######################

仿真后得到的lib文件

/******************************************************************************/

/* Liberty models generated by SiliconSmart N-2017.12-SP2 build date: Jun 01, 2018 10:40:28. (SMSC-2) */

/* Siliconsmart Path: /export/SoftWare/Synopsys/siliconsmart/N-2017.12-SP2/linux64/bin/siliconsmart */

/* Host Name: icpc, User Name: master, PID: 13639 */

/* Directory: /home/master/Work/smic18inv */

/* */

/* File generated on Sun Dec 18 12:01:49 CST 2022. (SMSC-3) */

/******************************************************************************/

library(tt_3p3v_25c) {

delay_model : table_lookup ;

library_features(report_delay_calculation, report_power_calculation);

time_unit : 1ns ;

voltage_unit : 1V ;

current_unit : 1mA ;

capacitive_load_unit(1, pf);

pulling_resistance_unit : 1ohm ;

leakage_power_unit : 1mW ;

input_threshold_pct_fall : 50 ;

input_threshold_pct_rise : 50 ;

output_threshold_pct_fall : 50 ;

output_threshold_pct_rise : 50 ;

slew_derate_from_library : 1 ;

slew_lower_threshold_pct_fall : 30 ;

slew_lower_threshold_pct_rise : 30 ;

slew_upper_threshold_pct_fall : 70 ;

slew_upper_threshold_pct_rise : 70 ;

nom_process : 1 ;

nom_temperature : 25 ;

nom_voltage : 3.3 ;

default_cell_leakage_power : 0 ;

default_fanout_load : 1 ;

default_inout_pin_cap : 9999 ;

default_input_pin_cap : 9999 ;

default_leakage_power_density : 0 ;

default_output_pin_cap : 0 ;

operating_conditions(tt_3p3v_25c) {

process : 1 ;

temperature : 25 ;

voltage : 3.3 ;

}

input_voltage(default) {

vil : 0 ;

vih : 3.3 ;

vimin : 0 ;

vimax : 3.3 ;

}

output_voltage(default) {

vol : 0 ;

voh : 3.3 ;

vomin : 0 ;

vomax : 3.3 ;

}

lu_table_template(ndw_ntin_nvolt_6x2) {

variable_1 : input_net_transition ;

variable_2 : normalized_voltage ;

index_1("1, 2, 3, 4, 5, 6");

index_2("1, 2");

}

lu_table_template(tmg_ntin_oload_6x6) {

variable_1 : input_net_transition ;

variable_2 : total_output_net_capacitance ;

index_1("1, 2, 3, 4, 5, 6");

index_2("1, 2, 3, 4, 5, 6");

}

power_lut_template(pwr_tin_oload_6x6) {

variable_1 : input_transition_time ;

variable_2 : total_output_net_capacitance ;

index_1("1, 2, 3, 4, 5, 6");

index_2("1, 2, 3, 4, 5, 6");

}

normalized_driver_waveform(ndw_ntin_nvolt_6x2) {

driver_waveform_name : "driver_waveform_default_fall" ;

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0, 1");

values("0, 0.05",\

"0, 0.2552",\

"0, 0.9754",\

"0, 2.351",\

"0, 4.493",\

"0, 7.5");

}

normalized_driver_waveform(ndw_ntin_nvolt_6x2) {

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0, 1");

values("0, 0.05",\

"0, 0.2552",\

"0, 0.9754",\

"0, 2.351",\

"0, 4.493",\

"0, 7.5");

}

normalized_driver_waveform(ndw_ntin_nvolt_6x2) {

driver_waveform_name : "driver_waveform_default_rise" ;

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0, 1");

values("0, 0.05",\

"0, 0.2552",\

"0, 0.9754",\

"0, 2.351",\

"0, 4.493",\

"0, 7.5");

}

cell(test_std_cell_inv) {

cell_leakage_power : 1.999e-05 ;

pin(Vin) {

capacitance : 0.01719 ;

direction : input ;

driver_waveform_rise : "driver_waveform_default_rise" ;

driver_waveform_fall : "driver_waveform_default_fall" ;

input_voltage : default ;

}

pin(Vout) {

direction : output ;

function : "(!Vin)" ;

min_capacitance : 0.001 ;

output_voltage : default ;

internal_power() {

related_pin : "Vin" ;

fall_power(pwr_tin_oload_6x6) {

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0.001, 0.01684, 0.07246, 0.1787, 0.3441, 0.5763");

values("-0.05146, 0.01897, -0.03637, -0.03105, -0.03326, -0.0346",\

"-0.04478, -0.03946, -0.0367, -0.03591, -0.03522, -0.03511",\

"-0.01487, -0.02017, -0.02676, -0.03026, -0.03108, -0.03288",\

"0.05642, 0.03629, 0.01238, -0.003069, -0.0132, -0.02017",\

"0.1708, 0.1417, 0.09344, 0.05786, 0.0327, 0.01608",\

"0.3339, 0.2975, 0.2271, 0.1658, 0.1195, 0.08601");

}

rise_power(pwr_tin_oload_6x6) {

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0.001, 0.01684, 0.07246, 0.1787, 0.3441, 0.5763");

values("0.1024, 0.1631, 0.1389, 0.14, 0.1441, 0.2",\

"0.1073, 0.1143, 0.1297, 0.1371, 0.1393, 0.1956",\

"0.143, 0.1368, 0.1318, 0.1329, 0.1387, 0.2014",\

"0.217, 0.2049, 0.1795, 0.1636, 0.1544, 0.2216",\

"0.333, 0.3146, 0.2786, 0.2406, 0.2112, 0.2833",\

"0.4969, 0.4739, 0.4275, 0.3707, 0.3196, 0.4108");

}

}

timing() {

related_pin : "Vin" ;

timing_sense : negative_unate ;

timing_type : combinational ;

cell_fall(tmg_ntin_oload_6x6) {

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0.001, 0.01684, 0.07246, 0.1787, 0.3441, 0.5763");

values("0.05316, 0.1278, 0.3543, 0.7828, 1.446, 2.384",\

"0.05924, 0.1473, 0.3727, 0.8013, 1.471, 2.405",\

"-0.01342, 0.1473, 0.4503, 0.8819, 1.549, 2.483",\

"-0.1942, 0.04396, 0.4847, 1.022, 1.702, 2.635",\

"-0.4994, -0.1872, 0.4063, 1.108, 1.913, 2.879",\

"-0.9428, -0.5576, 0.1853, 1.074, 2.059, 3.158");

}

cell_rise(tmg_ntin_oload_6x6) {

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0.001, 0.01684, 0.07246, 0.1787, 0.3441, 0.5763");

values("0.1148, 0.3877, 1.151, 2.568, 4.768, 7.874",\

"0.1582, 0.3835, 1.161, 2.588, 4.786, 7.885",\

"0.3087, 0.5512, 1.278, 2.69, 4.9, 7.981",\

"0.5728, 0.8771, 1.604, 2.973, 5.147, 8.223",\

"0.9636, 1.344, 2.163, 3.494, 5.611, 8.638",\

"1.492, 1.958, 2.892, 4.27, 6.345, 9.326");

}

fall_transition(tmg_ntin_oload_6x6) {

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0.001, 0.01684, 0.07246, 0.1787, 0.3441, 0.5763");

values("0.01839, 0.07828, 0.2896, 0.6914, 1.316, 2.193",\

"0.02623, 0.08043, 0.2896, 0.6898, 1.314, 2.192",\

"0.05379, 0.1328, 0.3134, 0.6911, 1.315, 2.189",\

"0.1037, 0.2199, 0.4203, 0.7518, 1.319, 2.193",\

"0.1709, 0.3391, 0.5861, 0.9251, 1.44, 2.212",\

"0.2551, 0.4819, 0.7956, 1.168, 1.671, 2.397");

}

rise_transition(tmg_ntin_oload_6x6) {

index_1("0.02, 0.1021, 0.3902, 0.9403, 1.797, 3");

index_2("0.001, 0.01684, 0.07246, 0.1787, 0.3441, 0.5763");

values("0.05818, 0.254, 0.9432, 2.258, 4.319, 7.197",\

"0.05832, 0.2543, 0.9425, 2.257, 4.31, 7.199",\

"0.08753, 0.2609, 0.9453, 2.258, 4.306, 7.193",\

"0.119, 0.3222, 0.9439, 2.257, 4.31, 7.173",\

"0.1634, 0.3886, 1, 2.258, 4.306, 7.18",\

"0.2152, 0.4817, 1.124, 2.293, 4.32, 7.178");

}

}

}

}

}