第一节 《CMOS集成电路后端设计与实战》

本节书摘来自华章出版社《CMOS集成电路后端设计与实战》一 书中的第3章,第3.3节,作者:刘峰,更多章节内容可以访问云栖社区“华章计算机”公众号查看。

3.3 标准单元设计流程

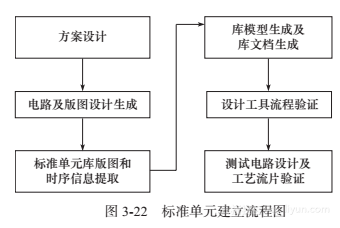

标准单元的设计流程是实现标准单元建库工作的基本指导方针,只有在一套完善且系统的开发流程下逐步完成每个工作环节才能实现标准单元库的建立。一般情况下,可以按照以下六大步骤完成CMOS标准单元库的开发工作,但在实际应用过程中由于种种原因,会出现开发工作的反复迭代,例如当工艺和互连线的器件模型不够精确时,引起单元特征化,得到的模型参数不够精确,就需要迭代。如图3-22所示为标准单元库实现的基本流程图。

1)方案设计。根据设计需求确定设计目标和实现方案。

2)电路及版图设计生成。标准单元库的主要参数定义后,就需要对各个种类的单元进行电路设计和版图实现。

3)标准单元库版图和时序信息提取。标准单元设计完成了单元的Schmatic和Layout视图后,通过对版图和时序信息进行提取才能被多种EDA工具所识别和使用。

4)库模型生成及库文档生成。标准单元库版图和时序信息都提取完成以后,就可以进行相关数据的整理和归纳,供后续设计使用。

5)设计工具流程验证。标准单元库的数据都准备好了以后,就可以供相关EDA工具使用,验证其数据在设计实现流程中是否可用。

6)测试电路设计及工艺流片验证。测试电路设计主要包括功能验证电路、工作频率测试电路、建立/保持时间测试电路、恢复/移除时间测试电路以及制定测试方案。

3.3.1 方案设计

标准单元库的设计在大方向上需要确定标准单元库的应用类型及各种类型库所需要包含的单元种类、数量及单元性能指标等。标准单元库中单元数量的多少、库的预期应用性能、库的开发成本,也是设计中应考虑的重要因素,在工程实现之前都需要规范。

3.3.1.1 标准单元电源/地线宽度的确定

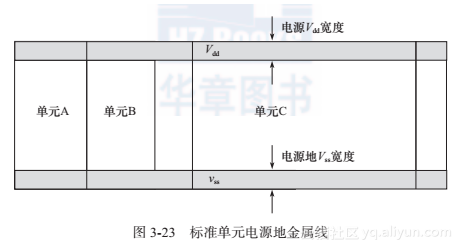

基于标准单元设计方法的设计,通过设置合适的单元电源线的金属宽度满足功耗分布的需要,同时电源线的宽度应该设计得尽量窄来减少电源线所占用的标准单元内部面积,以实现最大化布线资源。

然而,标准单元的电源线宽度首先需要设计的足够宽来满足自身需要。对于给定的具体设计,我们确定合理的电源/地线的宽度主要是为了防止因温度、电流密度等因素引起的电迁移。

标准单元电源/地线宽度的确定可以通过下面3种设计建议的方法来预估和确定。

1)直接参考工艺厂家的标准单元库进行定义。如果在本工艺下有相应工艺厂家的标准单元库,可以直接套用该标准单元中电源/地线的宽度。

2)基于标准单元仿真实验数据进行定义。根据仿真实验数据自行定义标准单元库电源/地线的宽度,确定电源/地线宽度的基本建议方法如下:

电迁移依赖于导体中电流的大小,而电迁移敏感的单元像输出缓冲器和时钟发生器一样的大驱动器。在确定标准单元的物理设计规范前,在大范围温度、供电电压、信号斜率和工艺偏差内对大驱动能力单元进行模拟,以获得流过单元电源地网络的导线电流的预估最大值,同时结合流片厂家的电流密度规则决定电源和地网络导线的最小宽度。

以驱动缓冲器BUFX20单元为模拟对象,在典型工艺下,做直流分析,电源Vdd电流特性如下:

假如由工艺规则文件的电流密度规则(Current Density Rule)规定在TT条件下,M1的最大DC电流假如是1mA/μm,则电源地网络导线最小宽度是:

WM1=0.3mA/1mA/μm=0.3μm

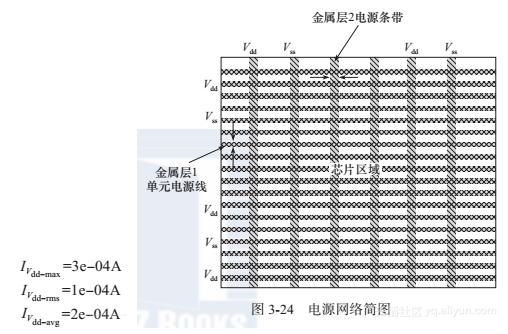

3)基于设计所预估的总功耗和面积信息来定义。下面的设计建议通过一些简单的假设提供比较粗略的预估,假设标准单元的电源线与金属层2的电源条带(stripe)连接,如图3-24

所示。

假定的参数说明如下:

Iavg——设计中的总平均电流,该值通过预估的总功耗计算得到;

dm1——金属层1能够允许的最大电流密度;

dm2——金属层2能够允许的最大电流密度;

Im1——水平方向上的金属层1可以提供的最大电流;

Istrap——金属层1电源线总共需要提供的最大电流;

Wm2——实现垂直电源带的金属层2的宽度;

r——实现垂直金属层2电源带的数目;

c——设计中标准单元电源线的预估总行数;Wm1——金属层1作为电源线的宽度。

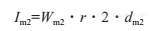

假设垂直方向上的金属层2的电流从金属线的两端流入,通过以下公式计算流过金属层2的电流:

同样假设标准单元金属层1电源线的电流也是从金属线两端流入,则金属层1电流线的电流计算公式如下所示。

最后根据金属层1电源线总共需要提供的最大电流和设计中标准单元电源线的预估总行数算出金属层1作为电源线的宽度,则电源线宽度的计算公式如下所示。

实际上还要考虑连接金属层1和金属层2的通孔个数问题。

3.3.1.2 标准单元高度的确定

确定合理的标准单元高度,不仅有利于进行高效的布局布线,还可以减少长距离导线互连带来的延时损失,对水平方向连线紧张的工艺尤为重要。

通过工程实践,总结两种方法如下:

1)如果在当前工艺下,有相应工艺厂家的标准单元库,可以直接套用该标准单元的高度。

2)可以根据实验数据自行定义标准单元库高度,下面推荐的基本粗略预估思路如下:

由于电子的载流子迁移率大于空穴的载流子迁移率(一般是两倍多),所以P管宽度一般比N管大,而或非门是N管并联,P管串联。在通用的标准单元库中,单倍四输入的或非门是所有单元中N管有源区最高的(五输入甚至更多的就选用输入最多的或非门),所以假设通过一个四输入NORX1门(保证有源区没有折叠管的最大值),通过固定的N管X1尺寸来确定P管非折叠高度,最终确定最小单元高度。最后根据版图设计规则和布线要求得到水平布线通道值后,结合四输入NOR门的高度最终确定单元高度等于几条布线通道值。通过对多个工艺下标准单元布线通道值的分析,一般的取值为7~15,所以标准单元的高度在通过或非门计算后,需尽量达到拥有7~15个布线通道的高度。

3.3.1.3 标准单元驱动强度的设置

为了满足实际需求,可以根据逻辑功能设计不同尺寸、不同驱动能力的单元。一般的逻辑单元都设计了至少四种不同驱动能力的单元:半倍驱动能力的低功耗单元、常用的单倍驱动能力单元、速度更快的2倍驱动能力单元和4倍驱动能力单元,用来满足不同的设计需要。而常用的反相器和时钟缓冲器设计了更多的驱动能力单元。其中,反相器一般会设计10种不同驱动能力的单元,用于时钟树的时钟反相器和缓冲器会设计从半倍到二十倍之间不同驱动能力的单元。

在定义驱动强度方法之前,首先应定义驱动强度最小单元的N管尺寸。下面推荐的基本粗略预估思路确定最小单元N管尺寸的方法如下:

根据版图设计规则中定义的接触孔(contact)大小和有源区最小包孔参数值,选择最小包孔的有源区宽度,即半倍(XL)驱动能力N管宽度。考虑到驱动能力,需要在实际的工程中作适当的放大。

这样介绍三种定义驱动强度的粗略方法。

1)零负载与倍数尺寸。该种驱动能力的定义方法首先是设定输出负载为0,即通过本征延时数据来定义不同驱动能力的单元。以N管最小尺寸为基数,通过扩大基数整数倍的尺寸定义相应的驱动单元(即尺寸通过以最后一级晶体管的最小尺寸为基数,再乘以一个倍数来定义驱动能力),同时按照设计要求规定上升和下降延时的最大偏差值,经过尺寸微调后达到要求即可。

2)倍数负载与固定延时。由于在前端逻辑综合时,综合软件是以延时、面积、功耗等约束进行单元选取。后端布局布线也是根据延时、负载等因素确定单元的选取。传统的零负载与倍数尺寸的方法不能有效地提高前端综合工具和后端布局布线工具对标准单元库的合理选择。因此倍数负载与固定延时的方法比零负载与倍数尺寸法更适合设计适用于EDA工具调用的标准单元库。

该类型驱动能力的定义方法是首先设定INVXL的输入负载为最小单元输出负载的基数值,根据单元驱动的倍数同时增加基数负载的相同倍数,即负载基数值与倍数相乘,不是使用相同驱动力倍数的INV的输入负载值。按照设计要求确定在该对应负载下的延时规定来设计相应驱动能力的标准单元,其延时规定可以定义上升和下降都需延时小于某个数值,并比同类型X1单元的延时偏差小于某个数值。

3)固定负载与降级延时。该方法主要用于添加中间驱动能力单元中。通常标准单元库提供了多种驱动能力(如X1,X2,X4,X8,X16)的单元。在固定负载下,依据延时设置单元的驱动力可以使工具对单元的选取具有更大的灵活性,相对传统方法更具针对性。

一般自动综合和布局布线后,EDA工具使用了大量小驱动能力的单元,可见在典型的设计中低驱动能力单元使用得很普遍。因此,提供延时间隔更短的低驱动能力单元显得更为重要。如果在现有标准单元数据中,INV单元在输入斜率和输出负载相同情况下,延时数据X1和X2间的延时差值比X4和X8间的延时差值大。在相同激励和负载情况下,对于驱动能力相近的单元,其延时与驱动能力近似为线性关系,延时随驱动能力增大而递减,为了提高标准单元库的灵活性,需要在XL~X1和XL~X2间根据延时差值增加更多驱动能力等级的单元,如驱动能力单元X0.6,X0.8,X1.3,X1.7等。

该类型驱动能力的定义方法以X1~X2之间的驱动设置为例,将倍数负载与固定延时方法中X2单元采用的负载作为X1.x系列单元的固定负载进行模拟,根据模拟结果确定线性关系的系数,从逐渐递减的单元延时参数中设定X1.3,X1.7等单元。

在设置标准单元驱动强度的同时还需要考虑标准单元电路最后一级P/N管宽长比,通常在标准单元库中可以把P/N管宽长比值分成两类。一类是作为构成时钟网络的标准单元P/N管宽长比值,该P/N管宽长比值主要考虑时钟网络标准单元需要平衡上升时间和下降时间。另一类是常规的为延时优化的P/N管宽度比值,该P/N管宽长比值主要考虑标准单元驱动力最优化。

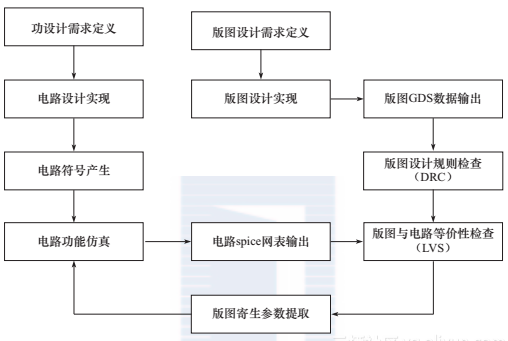

3.3.2 标准单元电路及版图设计

在定义了标准单元库的主要设计参数后,就需要对各个种类的单元进行电路设计和版图实现。

在标准单元库中,复杂的逻辑单元(例如多路选择器、异或/同或门等)通常含有较多的晶体管数目,对复杂逻辑单元的电路结构进行设计和优化,相比版图能获得更好的效果。静态CMOS工作时速度慢,动态电路类型可能是最快的实现结构,基于传输管和传输门的电路通常被认为是快速且低功耗的。在电路级,利用各种电路实现技术对各单元进行合理的设计,对后期单元库的整体性能起决定性作用。

标准单元电路及版图设计基本流程如图3-25所示。

最终标准单元库是提供给布局布线工具使用的,而不是人工手动布局,所以在标准单元的版图实现上要尽可能的符合布局布线工具的要求,使布局布线工具合理地分配单元位置并提供最多的布线资源以达到系统整体性能最优。

下面归纳在版图实现中,一直要遵循的几个基本设计建议。

1)输入输出端口要尽可能地放置在网格格点上,水平和垂直方向上的端口应尽量错开,这样可以充分利用垂直布线的资源。

2)输入输出端口必须在本单元的边界以内,而且边缘端口必须和单元的边界保持至少半个最小格点间距。

3)对于输入输出端口比较密集的单元,稍微增加单元面积的大小有时会比刻意保持单元面积最小要好,这样可以增加布线资源。

4)保证同类型的单元中最大单元的宽度是最小单元宽度的10倍之内。如果单元很复杂,可以通过增加高度来保证宽度的要求。

5)所有单元的宽度必须是格点间距的倍数或者是偏移半个格点后网格的倍数(根据布线工具的策略来定)。

6)如果单元内输入输出端口的周围有剩余空间,可以增加端口的金属面积使其更具多通孔性,多通孔单元可提高可连接度。

3.3.3 标准单元库版图和时序信息的提取

设计的标准单元库在DRC、LVS及ERC确定版图没有错误后,就可以进行物理信息抽象化来提取Lef文件了。Lef文件用于后端布局布线,它包含标准单元的物理视图信息(PIN、boundary、metal)。提取Lef文件需要准备的数据是GDSII版图数据和包含布局布线信息的工艺文件。Lef文件包含了单元的金属层、PIN及电源地信息,此外还有单元的面积和单元间的拼接信息。

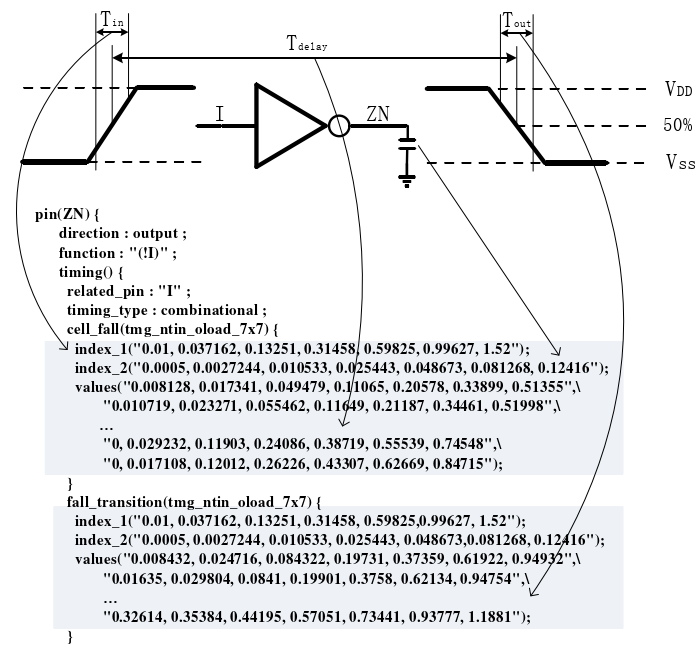

标准单元设计完成了单元的Schmatic和Layout视图后,但单元输入负载、速度和功耗等信息却没有以时序分析工具能认知的形式提取出来,例如综合工具需要知道单元的逻辑功能、单元实际的输入负载电容、在不同输入斜率和输出负载情况下单元的延时和功耗、单元的面积等。因此标准单元必须完成时序信息特征化(提取.lib文件)后,才能被多种时序分析工具所识别和使用。单元时序信息特征化就是通过模拟仿真器来提取标准单元相关时序信息的过程。

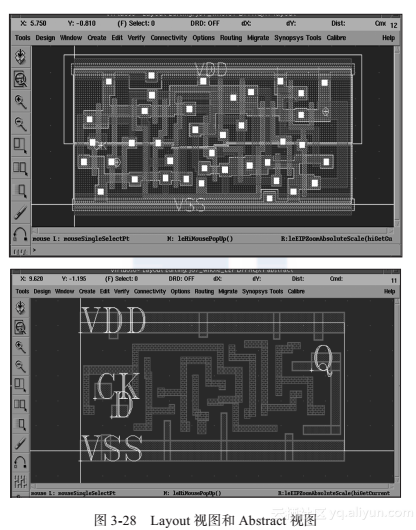

3.3.3.1 版图物理信息Lef文件的提取

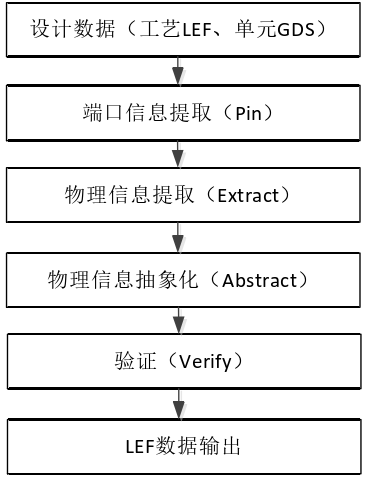

在DRC、LVS及ERC确定版图没有错误后,就可以提取Lef文件了。Lef文件用于后端布局布线,它包含标准单元的物理视图信息(PIN、boundary、metal)。业界一般使用Cadence公司的Abstract Genetrator来提取Lef信息,基本提取流程如图3-26所示。

提取Lef文件需要准备的数据是GDSII版图数据和包含布局布线信息的工艺文件。

用Virtuoso将标准单元的GDSII数据导入一个Library,打开Abstract Genetrator并连接Library,界面如图3-27所示。为防止Abstract软件错误识别标准单元的PIN信息,需要导入标准单元的逻辑功能网表文件。

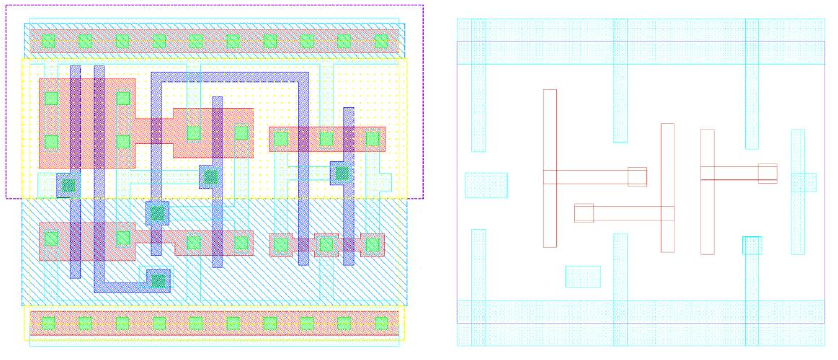

以触发器单元DFFHQX1为例,Layout视图和提取Lef信息并导入Virtuoso后得到Abstract视图如图3-28所示。Lef文件包含了单元的Metal1、PIN及电源地信息,此外还有单元的面积和单元间的拼接信息。

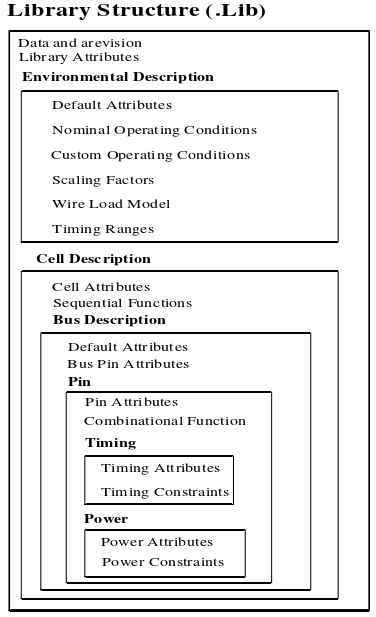

3.3.3.2 时序信息Lib的提取

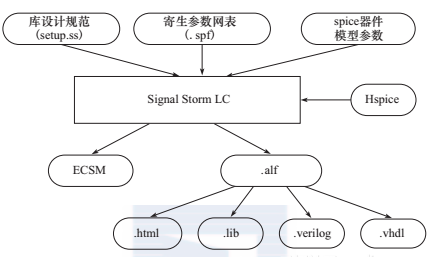

标准单元必须完成时序信息特征化(提取.lib文件)后才能被多种时序分析工具所识别和使用(可参考视频:数模混合芯片后端文件说明)。业界使用特性参数提取的工具主要是Cadence公司的SignalStorm Library Characterizer(目前嵌入到ETS软件中)、已被收购的Magma公司的Siliconsmart和synopsys的NCX。

这里以早期Cadence公司的SignalStorm Library Characterizer为例简单介绍,不管该软件版本及名称如何变化,但其工作大体流程基本不变。

SignalStormLC(SignalStorm Library Characterizer)可提取标准单元(数字的)和IO端口的时序信息,并将其整合为.lib文件。典型的时序信息特征化流程,如图3-29所示。

将库设计规范文件(setup.ss)、标准单元的带寄生参数网表文件(.spf)及Hspice器件仿真模型参数文件(.lib和.mdl)输入到SignalStormLC中,内部机制调用Hspice进行模拟,可得到标准单元的有效电流源模型文件(ECSM)及中间文件(.alf),中间文件(.spf)可转化为多种数据格式(包括.html、.lib、.verilog和.vhdl),供其他相关EDA工具使用。

使用SignalstormLC提取时序信息需要一些必要的命令语句。可将这些命令编写到一个脚本文件(.txt或者其他后缀)中,将软件启动后,调入文件即可等待.lib文件的生成。

3.3.4 库模型与库文档生成

标准单元库版图和时序信息都提取完以后,就可以进行相关数据的整理和归纳了。库模型需要整理归纳的基本数据如下:

1)标准单元库各个单元数据的文字描述文档。

2)标准单元库的Verilog代码数据、电路级(CDL)数据、物理版图(GDSII)数据、物理视图(Lef)数据及时序(LIB)信息数据。这些数据再结合厂家的工艺文件数据就可以供相关EDA工具进行工程应用了。

3)指导性文档。当标准单元库完成以后,需要对其进行性能的评估,总结该标准单元库适合使用的环境数据,指导使用者在该单元库性能指标达到的前提下,合理地设计系统来实现预期的目标。其中最重要的一个指导性数据是使用该单元库可以使系统达到什么样的性能,即最小时钟周期的设置。

一种对标准单元库进行性能预估的可行性理论方法如下:

在ITRS(国际半导体技术发展路线图)中,为了建立一个微处理器时钟频率的趋势模型采用了一种概念,即时钟速度不能超过固定数量的门的传播延时。例如在2001年的ITRS中,一个16级的典型门延时被定义为全局时钟周期,而一个典型的门延时则指的是一个FO4(Fanout-of-4 Inverter Delay)。目前FO4作为一种延时单位被广泛采用,这样做的好处是在讨论体系结构如何影响性能时可以把工艺的因素放在一边。

在过去的十多年中,微处理器的时钟周期大幅下降。例如,Intel的6代X86微处理器的时钟周期从1992年的53FO4(i486DX2)下降到2002年的12FO4(Pentium4)。目前有研究指出,当同时考虑高性能和低功耗时,时钟周期为18FO4时,性能达到最优值。

所以根据这个指导思想,通过测试标准单元库所采用工艺的FO4值,确定使用该标准单元库后系统的最优频率值,可以指导设计者对系统进行合理的性能定义。

如果选取某工艺典型情况下,反相器的平均传输延时作为该工艺的FO4参考值55.36ps,根据时钟周期为18FO4时性能最优的结论得出:

T=18FO4=18×55.36ps=996.48ps

计算结果显示系统设计的最优时钟周期为1ns左右,工作频率1GHz左右。

通过对比该工艺厂家提供的时钟最小宽度数据和厂家标称可以达到的性能说明,该预估的时钟频率在这些数据范围之内,所以具有一定的参考价值。

3.3.5 设计工具流程验证

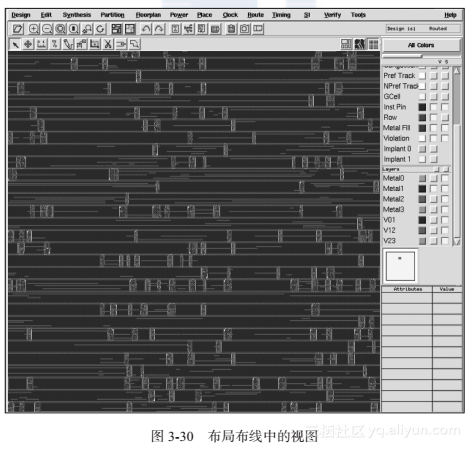

标准单元库的数据都准备好了以后,就可以供相关EDA工具使用,验证其数据是否可用。标准单元库的物理视图数据导入布局布线工具中的使用情况如图3-30所示。

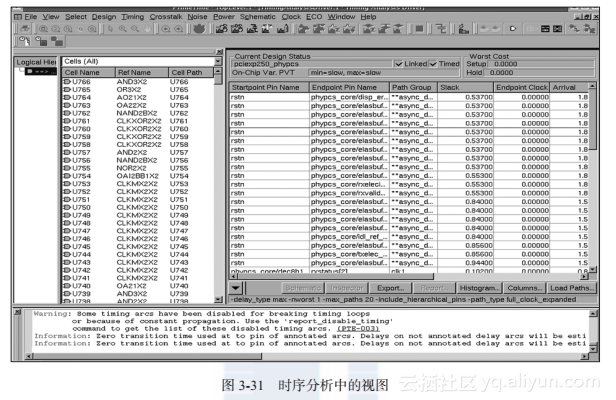

标准单元库的时序信息导入时序分析工具中的使用情况如图3-31所示。

3.3.6 测试电路设计及工艺流片验证

测试电路设计主要包括功能验证电路、工作频率测试电路、建立/保持时间测试电路、恢复/移除时间测试电路以及制定测试方案。

其他参考

第二节 亚阈值数字标准单元库设计 史兴荣 何进 张九柏 张子骥 贺雅娟,电子科技大学电子科学与工程学院(成都 610054)基于近/亚阈值标准单元库的数字集成电路设计与研究 史兴荣

基于对0.18 μm标准CMOS工艺的研究,本文设计了一套完备的电源电压为0.4 V的亚阈值数字标准单元库。设计流程包括工艺研究与方案设计、单元设计与物理实现、库文件的提取以及单元库验证。提出了传统沟道宽度调节与沟长偏置相结合的尺寸调整策略,有效增强PMOS管驱动并减小漏电流,提升库单元稳定性。利用ISCAS基准测试电路完成亚阈值标准单元库的验证,0.4 V电压下,相同设计,基于亚阈值数字标准单元库的设计的相比于基于商用库的设计,能耗减小20%以上,数据延时也有所减小,即亚阈值标准单元库性能明显优于商用库相比。

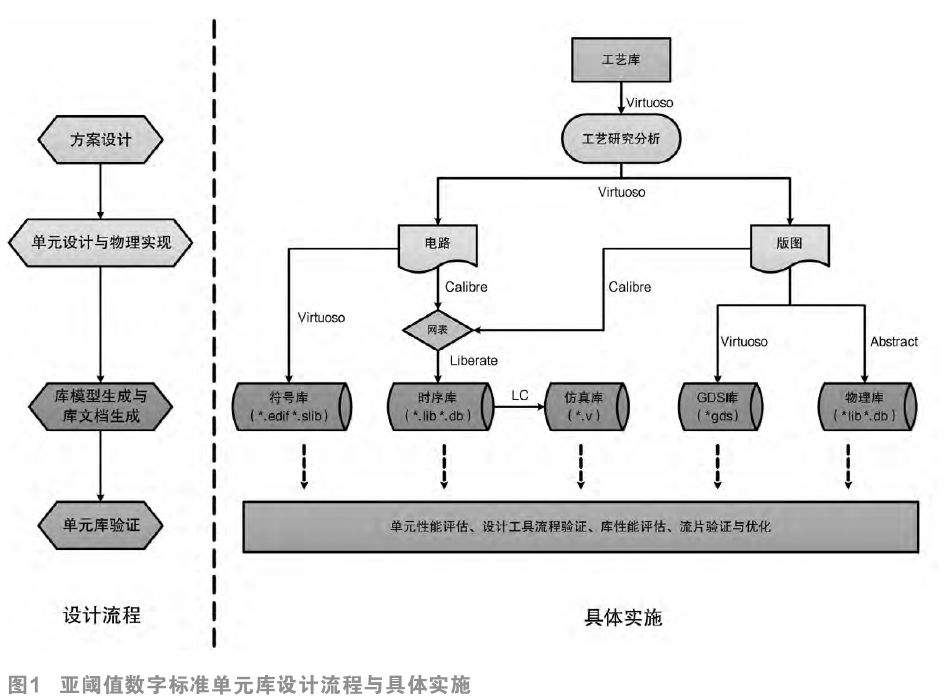

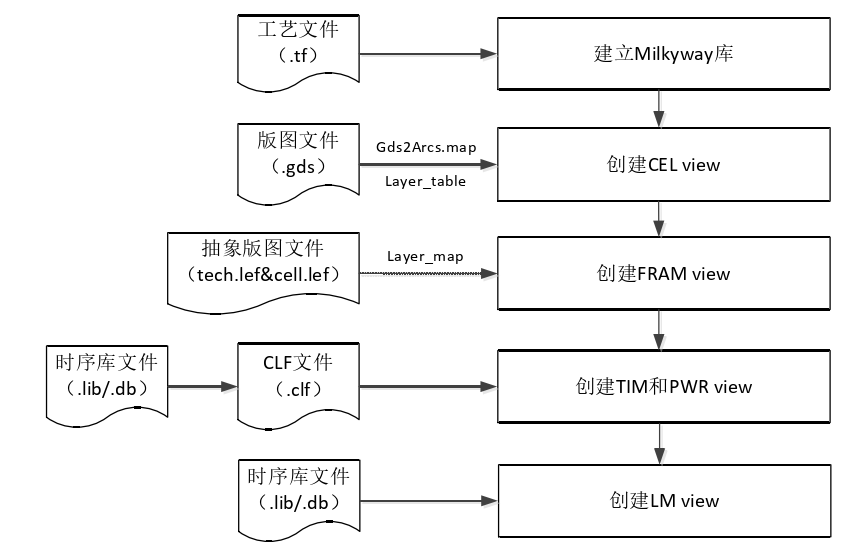

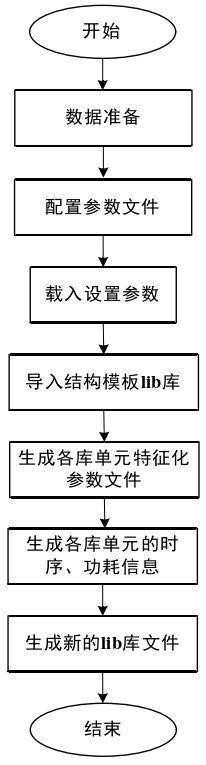

图1所示是本次亚阈值数字标准单元库设计的流程及具体实施示意图,在电路设计前,首先了解和研究该工艺的基本特性,包括晶体管电流电压特性、器件的漏极电流等参数随沟道长度和沟道宽度的 变 化 情 况 , 以及PMOS和NMOS的驱动强弱等,这些基于Virtuoso完成 。 其 次 , 基 于Virtuoso平台完成工艺研究分析以及电 路 图 版 图 的 设计,并基于Calibre完成单元电路网表的提取。然后,利用Liberate基于单元网表完成时序库建模,基于版图用Abstract完成物理库建模,用Library Compiler完成仿真库文件的生成,以及符号库、时序库和物理库文件的格式转换。最后,用综合和布局布线工具实现基准电路的设计,完成亚阈值库的验证工作。

3.2.2 时序库的建立

在完成标准单元的电路设计和版图设计之后,电路的具体工作性能如何我们并不知道,只有通过仿真才能知晓。而综合工具以及时序分析工具需要知道单元的逻辑功能、输入负载电容、不同输入斜率和输出负载情况下的单元延时和功耗信息才能对电路进行评估分析,并根据分析结果完成电路优化。这就需要建立时序库。 时序库的的建立即标准单元库的时序特征化,就是指时序库文件的提取工作,利用单元库特征化工具提取标准单元库的时序和功耗信息。业界主要的特征化工具有Cadence公司开发的 Liberate、已被 Synopsys 收购的Magma公司的 Siliconsmart以及 Synopsys 公司的 Liberty_NCX。下面我们就以 Cadence 公司的 Liberate 为例,说明时序信息的特征化。

Liberate 工具的典型标准单元特征化流程如图 3-6 所示,将库中单元的带寄生参数网表文件(.spf)、工艺库器件的 spice 仿真模型、库模板文件(template)以及软件的配置文件(setup)输入到 Liberate 中,Liberate 会基于配置文件的设置,调用仿真工具 Hspice 依照 template 中的要求对单元进行仿真,得到所需数据并整理形成规范的时序库文件(.lib),可以用 Library Compiler 完成.lib 格式到.db 格式的转换。

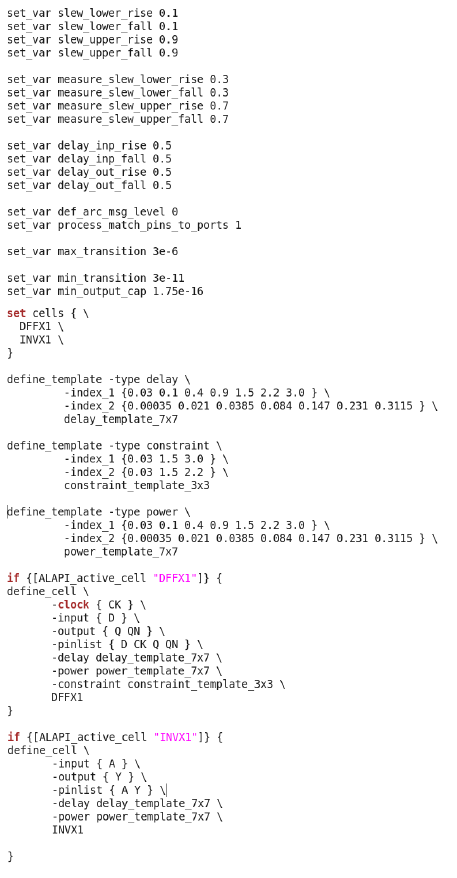

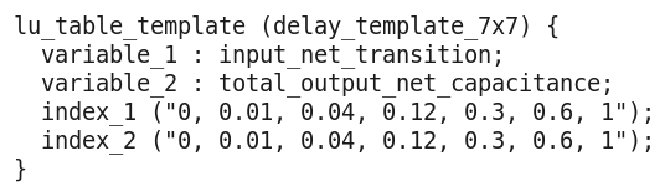

带寄生参数网表文件,在完成单元电路图和版图设计后由工具 Calibre 导出。器件 spice 仿真模型由工艺厂商提供,其中了提供 tt、ff、ss 等多个工艺角的器件特性,在调用器件模型时,需要指明所调用器件的工艺角。 模板文件(template)的内容可以分为两部分:整个库的模板和单元的模板。整个库的模板定义了时序库文件中的一些全局参数,如单元上升、下降时间、单元延时的定义及具体测试方式,库中最大、最小转换时间及最大负载电容等。单元的模板则是定义了每个单元相关的参数,包含单元的输入、输出端口定义,延时、时序约束和功耗的查找表模板等。如图 3-7 所示,是一个只包含两个单元的库模板文件。模板文件需要手写得到,当单元数目较多时工作量较大。当只是对原有库中的单元进行重新特征化时,可以直接利用特征化工具从原有的库中提取出模板文件,然后对模板中的部分内容进行修改即可。

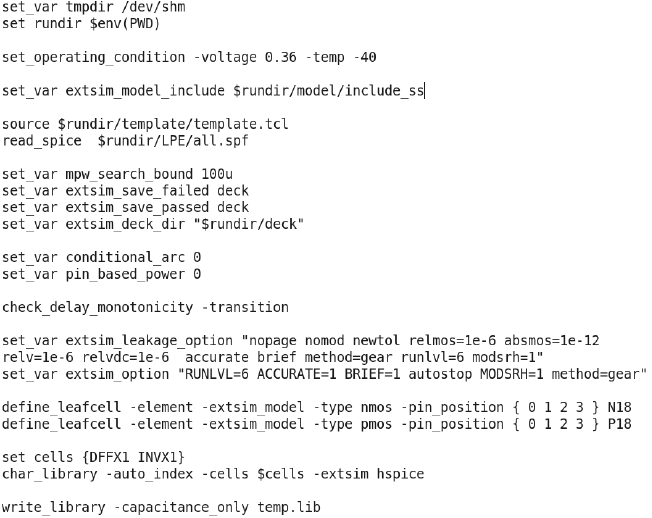

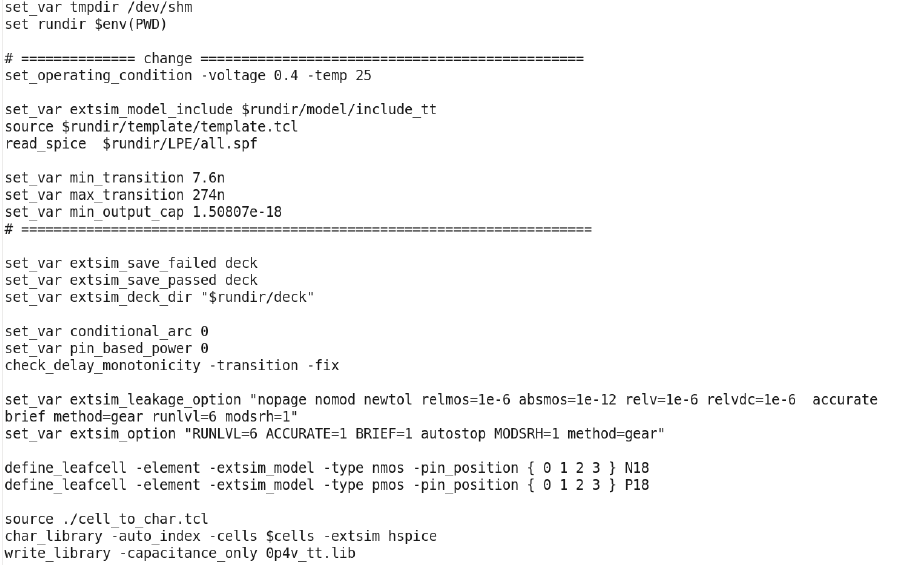

软件的配置文件就是特征化的过程控制设置文件,Liberate 内部有很多特征化相关的变量,set_var 命令就是对这些变量进行设置,赋其所需的值达到对软件的配置作用,是配置文件中使用最多的命令。如图 3-8 所示,其中包含了对临时文件的存储位置,最小脉冲宽度的范围设置,仿真结果的存储形式,器件 spice 仿真模型的导入,功耗的处理方式,外部仿真工具的仿真设置以及漏电仿真设置等。除了图中这些,其实对库中的电容、延时等其他所有信息的仿真及仿真结果的处理都可以进行设置。命令 set_operating_condition 是设置单元库的电压与温度,即仿真环境设置。用 source 命令完成单元库模板文件的载入,read_spice 命令载入库单元的带寄生参数网表文件,可以用.include 命令将其所有单元的网表载入到一个文件当中用于读取。同 skill 语言,set 完成变量的定义。命令 char_library 是特征化命令,后面可以加入各种设置,-auto_index 是指查找表的 index 是自动生成,-cells是所包含的单元设置,默认包含所有单元,图中只特征化两个单元,-extsim 指明是调用外部仿真软件 hspice 进行仿真。最后是 write_library 完成最后库的生成,同样可以进行相关的设置,包括数据的选择及显示形式等。

.2.3 物理库的建立

物理库是指单元库中所有单元的版图以及由版图生成的用于版图规划、自动布局布线的版图抽象文件。本章节,我们将详细介绍 Milkyway 格式的物理库的生成过程,从图中可以看出,基于物理版图首先导出 GDSII 文件,通过版图生成版图抽象文件 LEF,最后由 GDSII 和 LEF 转换成 Milkyway 格式的物理库。

3.2.3.1 LEF 文件的提取

LEF(Library Extract Format)是工具自动布局、布线所需的库文件,是版图的简化文件,提高布局布线的效率。LEF 文件包含标准单元的物理视图信息,有端口(Pin)、单元边界(Boundary)和金属层(Metal Layer)。LEF 的提取一般用 Cadence 公司的 Abstract Generator 完成,基本流程如图 3-9 所示:

(1)设计数据载入。包括工艺库的 LEF 文件和单元的 GDS 文件,工艺库 LEF文件包含工艺信息、设计规则信息、通孔信息等,为 GDS 的导入提供基础。单元的 GDS 文件是版图的 GDSII 数据文件,包含单元版图的所有信息。导入 GDS 文件时需要加载 GDSII 与 LEF 的图层定义文件(.map)。

(2)端口信息提取。手动设置单元的端口(Pin)和单元边界(Boundary)。绘制版图时加入了 Border 层作为版图边界,因此此时直接选定 Border 层设置边界即可。

(3)物理信息提取。设置需要提取的图层,所有信号 Pin 和电源 Pin 的 lable图层都需要选定。当只用到 Metal1 时,只需选中 Metal1。当用到多层金属时,需要选中其金属层及层之间的 Via 层。此外也包括对天线效应的估算信息提取设置。

(4)物理信息抽象化。需要设置电源轨线的位置及宽度,指定单元的 site 为coresite。对于 Blockage,有 Pin 和无 Pin 的金属层抽取出来的形式是不一样的,带Pin 的金属抽取出来是 dg 格式,不带 Pin 的金属抽取出来是 be 格式。

(5)验证。验证的目的是对抽象视图进行正确性检查。

(6)LEF 数据导出。File-Export-LEF 命令导出 LEF 数据。

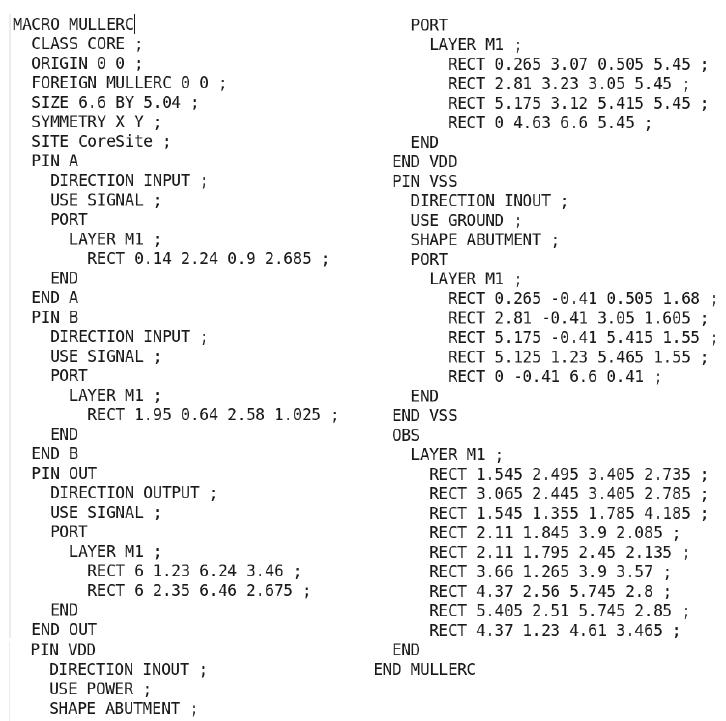

导出的单元 LEF 文件可以直接打开,内容如图 3-10 所示,可以看出,包含单元的面积,Pin 端口、电源和地的形状,也包含单元内部金属 blockage。将其导入到版图工具中可以看出,其中确实只包含 pin、Boundary 和 Metal layer 的视图。LEF与 GDS 的视图对比如图 3-11 所示。

3.2.3.2 Milkyway 库的生成

Milkyway 库包含多个视图,其中物理的视图包含 CEL 视图和 FRAM 视图,CEL 视图是完整的版图(Layout),FRAM 视图是抽象化的版图。版图的 GDSII文件就包含 layout 的所有信息,因此 CEL 视图可以由 GDSII 创建,由上小节可知,LEF 文件是单元版图的简化,因此用来完成 FRAM 视图的创建。此外,有的Milkyway 库中还包含有关时间和功耗信息的视图,有 TIM 视图、PWR 视图和 LM视图。具体的 Milkyway 库的创建流程如图 3-12 所示。

首先导入工艺文件(techfile,.tf),创建一个新的 Milkyway 库。其次载入库的版图文件(.gds),生成 CEL 视图,在导入的过程中需要两个文件单元类型定义文件和图层定义文件,Gds2Arcs.map 是单元类型定义文件,指定了哪些单元是FILLER 单元,哪些单元是标准逻辑单元。layer_table 文件是图层定义文件,用于工具对图层的识别。

2.2 晶体管电流电压特性

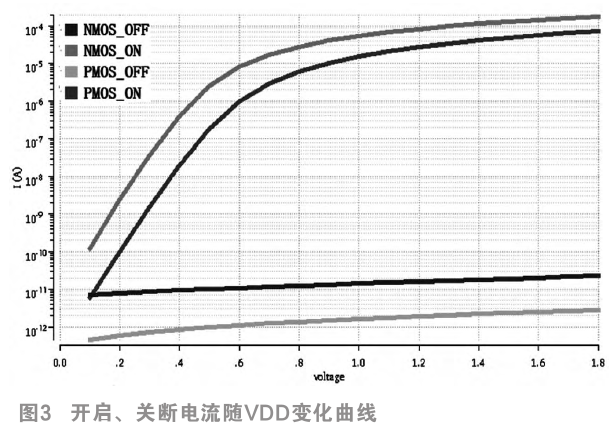

NMOS和PMOS的驱动能力是不一样的,即存在不匹配,在标准电压下(即超阈值电压),NMOS的驱动能力约为PMOS驱动能力的两倍,这得益于电子迁移率为空穴迁移率两倍多,在建立标准单元库时,单元设计时就要考虑到NMOS/PMOS失配,通过尺寸调节来实现单元的上拉下拉匹配。但是在亚阈值电压下,由MOS模型分析可知,NMOS/PMOS失配会增大,因此将商用标准单元库运用到低压电路中,电路性能会严重下降,会出现噪声容限下降,抗工艺波动能力下降,甚至逻辑误判导致电路无法正常工作等。

对相同尺寸的NMOS管和PMOS管进行仿真,晶体管的开启电流和关断电流随电源电压的变化曲线,如图3所示,随着电源电压的不断减小,NMOS管和PMOS管的开启电流和关断电流都不断减小,但是NMOS与PMOS的开启电流之比却在不断增大,在电压为0.4 V时,大尺寸管PMOS/NMOS开启电流比已接近于7,而对于最小尺寸管,甚至高达20,即PMOS和NMOS存在严重的不匹配,这给我们标准单元设计时上拉下拉平衡造成很大困难。

4.4.1 时序库文件的生成

时序库文件的生成就是主要是时序特征化的过程, 按照第三章所述的时序库建立流程实现。在准备好带寄生参数网表后,就是特征化配置文件的设置与单元库模板的编写。其中最重要的是单元模板中查找表模板中的变量 index 值的确定,变量 index 的范围以及取值直接影响电路仿真时对电路性能的估算准确度,范围太小,查找表不能覆盖全部实际情况,范围太大,覆盖范围广,但查找表只有 7*7=49个数据,严重影响估算偏差,因此 index 的确定对单元时序库的性能至关重要。

Index 的取值范围由库中单元来确定,而内部的具体取值不是均匀插入的,而是采用几何插值法确定,这样可以提升查找表电路仿真时插值估算的准确性。几何插值的比例相对比较固定,因此我们每个单元都采用固定比例(几何插值比例)的查找表模板,如下图 4-10 所示,是查找表模板的定义。

查找表中包含两个变量,上升/下降时间(input_net_transition)和输出负载(total_output_net_capacitance),可以看出,每个变量的值是(0,0.01,0.04,0.12,0.3,0.6,1),0 代表最小值,1 代表最大值,在实际仿真时,只需确定最小值和最大值,中间值按比例插入即可。整个库的上升/下降时间 index 是一定的,最大上升/下降时间是库中最小驱动反相器单元 INVXL 驱动最大驱动反相器单元INVX8 时的上升/下降时间,最小上升/下降时间是库中最大驱动反相器单元 INVX8驱动最小驱动反相器单元 INVXL 时的上升/下降时间。输出负载的 index 值,每个单元都不一样,最小负载值为库中所有单元的最小输入电容,最大负载值是本单元驱动固定负载其输出上升/下降时间达到最大值时的负载值。因此在特征化之前,必须先仿真得到 transition 的 index 值,以及预特征化得到单元的输入电容信息。

Typical 库的单元特征化配置文件如图 4-11 所示,其中,两个备注行(以#开头)之间的内容,包含 PVT 条件的设置和最大、最小上升/下降时间和最小电容的设置。在特征化 Fast、Slow 和 Slowa 库时需要做相应的改动,其余设置可以保持不变。Char_library 后加了-auto_index 的设置,如前面所述,结合最大、最小 transition及比例自动生成 transition 的 index 值,通过最大 transision 确定单元最大输出负载并实现 index 自动插值。

在特征化生成的.lib 文件信息还不够全,我们需要做完善处理,添加以及修改的内容主要以下包含三部分:

1)添加面积信息。单元面积默认为 0,需要从 LEF 文件中获取,并添加到.lib文件中。

2)添加 footprint。设置单元的 footprint,实现时序优化时相同逻辑不同驱动单元之间的替换。通常格式为:“cell_footprint:逻辑名”,比如两输入与非门的格式为:“cell_footprint:nand2”。

3)添加线负载模型。线负载模型用于电路综合时电路分析,主要是对信号线寄生效应的考虑,可以直接用商用库中提供的负载模型。

由于单元较多,方便起见,都是通过编写脚本自动化添加修改。添加完上述内容后,完整的时序库文件就完成了,再通过 Library Compiler 转换成.db 格式以及生成仿真库文件即可。.lib 文件部分内容如图 4-12 所示,其中的 foot_print 和 area信息都是在特征化后利用脚本添加的。

根据单元库的要求以及工艺角和温度对单元特性的影响,分别在四种 PVT 条件下完成单元特征化,如下表所示。工艺角选用 TT、FF 和 SS,由于温度反型效应,Fast 库温度为 125℃,Slow 库包含 0℃和-40℃两个温度。电压也是考虑了 10%波动的影响。

第三节 基于统计静态时序分析的低电压电路表征及设计优化(刘志远)东南大学硕士论文

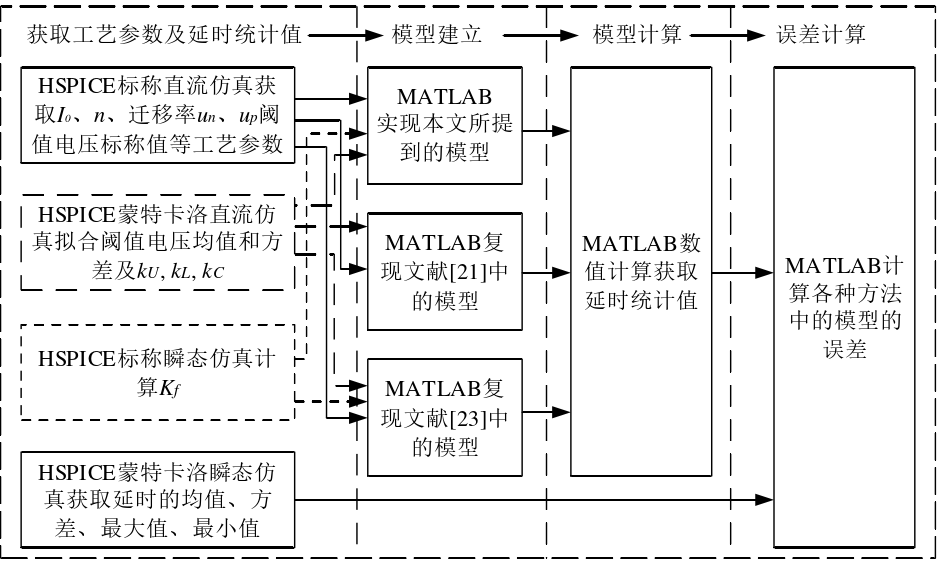

本节介绍统计分布模型的验证环境及过程,它们总结在图 5-1 之中,可分为四个阶段,即获取工艺参数及实际的延时统计值,模型建立,模型计算及最终的误差计算。此过 程 中 所 有 涉 及 的 蒙 特 卡 洛 仿 真 的 次 数 均 定 为 10000 次 , 验 证 过 程 使 用 了TSMC_28nm_HPC+工艺,由于尺寸越小的单元受工艺参数波动的影响越大,故本文选取了最小尺寸的单元进行验证,输出节点的负载为 FO4,所验证的单元的供电电压为亚阈值电压 0.25V,及近阈值电压 0.35V 和 0.45V,工作环境为 25℃,TT 工艺角。

第一个阶段为通过 SPICE 仿真获取工艺参数及真实的延时统计值,用于后续模型的建立及误差计算。其中,工艺参数 I0,n,迁移率 un,up 等可以通过使用式(2.3)所提到的跨阈值电流模型来拟合 HSPICE 标称直流仿真的结果而获得。对于延时标称模型(2.6)中的 Kf,可通过一次 HSPICE 标称瞬态仿真获得。阈值电压的均值、方差及式(3.11)的系数项需要通过拟合 HSPICE 蒙特卡洛直流仿真的结果而获得。最后,通过 HSPICE 蒙特卡洛瞬态仿真可以获得标准单元延时的统计值,如均值、方差、±3σ 值等,用于第四阶段中的模型误差的计算。

第二个阶段为模型的建立,在获取了工艺参数及一些拟合常量之后,可通过第三章所提到的流程建立相应的反相器结构、堆叠结构、并联结构以及传播延时的统计分布模型,同时可复现文献[21]和[23]的统计分布模型形成对比,其中文献[21]仅提到了反相器及堆叠结构的建模方法,文献[23]提到了反相器结构、堆叠结构及并联结构,但传播延时的统计分布模型均未在两篇文章提及,故传播延时的统计分布模型只与 SPICE 的仿真结果对比。

第三个阶段是使用模型计算出相应的分布参数,进而获得本文及其它两篇对比文献中延时分布的 PDF、均值、方差及±3σ 值,这些指标作为本文的对比对象,将在 5.2 中给出。

第四个阶段是对模型计算出的统计值与实际 SPICE 蒙特卡洛仿真所获得的统计值进行对比,体现出本文所涉及模型的优势,并进一步验证第二章分析中所提到的另外两篇文献中的模型的不足。

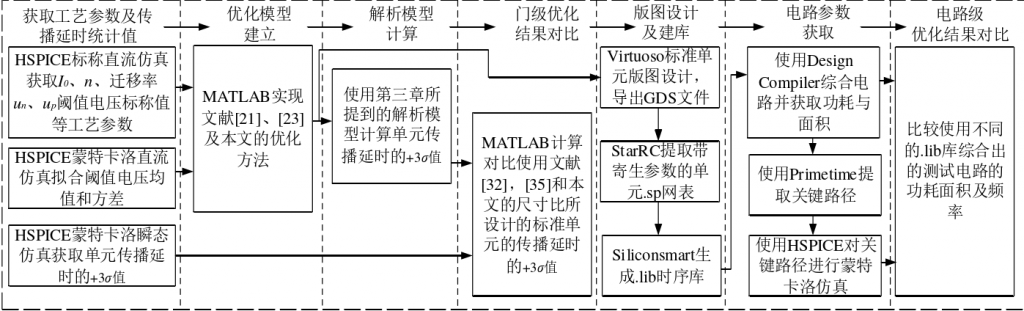

5.1.2 优化方法验证环境及过程

本节介绍标准单元延时+3σ 值优化效果的验证环境及过程,可粗略的分为版图前后两个阶段。它们总结在图 5-2 之中,总的步骤包括获取工艺参数及实际的传播延时统计值,建立优化模型获取最优尺寸比,解析模型计算对应尺寸比下的传播延时的+3σ 值,与另外两篇参考文献进行门级优化效果的对比,在进行版图设计及建库,获取电路参数后,进行电路级的优化结果对比。考虑到本文与文献[32]和[35]所推导出的尺寸比不同,为了确保对比的公正性,在验证过程中所有指标的对比均以所设计的标准单元最终的面积值相同为前提。同样地,此过程中所有涉及的蒙特卡洛仿真的次数均定为 10000 次,

验证过程使用了 TSMC_28nm_HPC+工艺,在版图前阶段的验证中对应的单元的供电电压为亚阈值电压 0.25V,及近阈值电压 0.35V 和 0.45V,工作环境为 25℃,TT 工艺角。而对于版图后建库的过程中则是。

获取工艺参数及实际的传播延时统计值的过程与上一节中的过程相同,在获取了这些工艺参数后,可分别得出文献[32, 35]以及本文所提出的优化方法下得出的最优尺寸比,然后可进行版图前标准单元传播延时的+3σ 值进行对比,由于在版图之前进行的是初步的对比,所以本文中对于版图前优化结果的验证选用的标准单元驱动为 1X,不再过多验证不同驱动大小的标准单元的优化效果。该验证过程中对于反相器,含有堆叠、并联结构的标准单元的传播延时的计算可以用到第三章所提到的模型以达到减少仿真量的目的,而对于剩余的一些复杂的单元,如 XOR2,XNOR2,AOI21D 等,由于第三章中没有给出相应的解析模型,此处仍然采用 SPICE 蒙特卡洛仿真来得出其传播延时的统计值。

在结束版图前的初步验证之后,根据优化模型所得出的最优尺寸比,本文使用Virtuoso 软件对所验证过的标准单元进行了版图的绘制,每种标准单元的驱动大小为 1X,2X,4X 及 8X,由于各种方法下的尺寸比不同,为了保证对比的公平性,故将最优尺寸比较小的情况下对应的 NMOS 管的宽度加大,以保证最后所画版图的面积相同。在绘制完版图后,通过导出 GDS 文件并读入到 starRC 软件中,可抽取到带寄生参数的标准单元 SPICE 网表。同时,准备其它建库所需的输入文件,本文中运用到的模板库为TSMC_28nm 工艺,0.9V,25℃,TT 工艺角,7T 低阈值标准单元的.lib 文件,晶体管模型为 TSMC_28nm 工艺中的 LVT 管模型,在准备好这些文件之后可将其读入 Siliconsmart中进行后续的标准单元的建库工作。在输出最终的.lib 文件前需要对其进行仿真配置,本文中,抽取的库文件对应的环境为 0.35V,25℃,TT 工艺角,查找表索引中负载的范围与模板库相同,输入波形过渡时间的取值范围则是取 FO4 负载下的最小尺寸反相器输出波形过渡时间的 0.1 倍和 10 倍。建库过程中仿真器使用了 HSPICE,驱动波形选取为 PWL 波。在做完仿真配置后可通过单元仿真输出所设计的传播延时+3σ 值最优的标准单元所对应的.lib 文件。

在绘制完版图并抽取出相应的标准单元库之后,则可从电路角度的对标准单元的优化效果进行验证,检验整体优化后的标准单元库带来的电路性能的提升。本文选取了ISCAS’89 系列测试电路,并使用 Design Compiler 对其进行综合得出功耗及面积的报告,为了提高时序报告的准确性,本文将综合后的 verilog 网表及.sdc 文件等读入到 Primetime中,通过仿真提取出 5 条关键路径,并对它们做 SPICE 蒙特卡洛仿真计算出受工艺参数波动影响,电路最坏情况下的工作频率,即频率的+3σ 值。在电路级的优化效果的对比上,本文选取了频率的+3σ 值,功耗,面积三个指标,与文献[32]和[35]进行对比。

第四节 采用SMIC 0.13um定制化工艺标准单元库的TOF芯片专用TDC模块设计

4.3.3 标准单元物理库的设计流程

设计标准单元的物理库使用的工具是 Synopsys 公司的 Milkyway 工具。 Milkyway的主要功能是转换版图数据,为 Synopsys 公司的工具提供物理库的数据。其物理库的数据去除了大量的版图内部信息,保留单元的框架、端口位置等版图的重要信息。设计标准单元物理库的主要步骤:

1)工艺文件的提取

在使用 Synopsys 公司的工具时,需要有工艺文件的支持。而在 4.2.2 节标准单元版图绘制时使用的工艺文件,是应用在 Cadence 工具的工艺格式文件。若需要使用在Synopsys 环境下的工具,需要重新获取一份 Synopsys 公司格式的工艺文件。获取Synopsys 工艺文件的途径有三种:第一是向工艺厂商购买获取,购买授权获得使用权,这种途径获取的工艺文件完整;第二种是自己编写,需要熟悉 Synopsys 公司的工艺文件的参数,撰写工艺文件的相关内容,这种途径获取工艺的工作量相对大,涉及的知识广;第三种途径就是通过 Milkyway 工具转换导入的版图的工艺文件,可以简易地将Cadence 环境下的工艺文件转换为 Synopsys 环境下的工艺文件。

论文采取的方法是第三种途径提取工艺文件,通过使用 Milkyway 工具导入标准单元的 LEF 文件来提取 LEF 文件中的工艺文件信息。

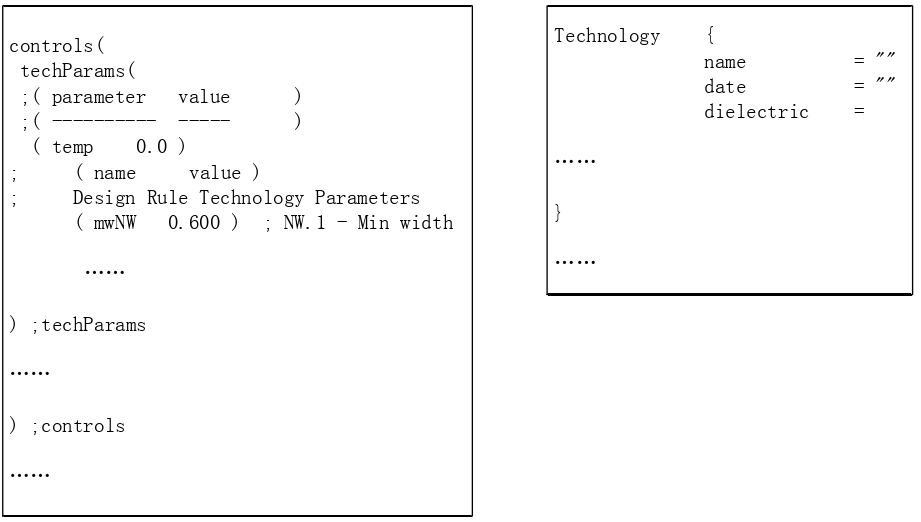

提取工艺文件时需要编辑 Cadence 公司的 Abstract Generator 工具导出的 LEF 文件。标准单元版图绘制后进行抽取后生成的 LEF 文件,包含了标准单元的版图信息以及工艺文件信息,需将两部分信息分别存放在工艺文件 LEF 文件和单元版图 LEF 中,并以LEF 文件的格式整理文件的格式存放,用于 Milkyway 工具的导入。图 4-16 为 LEF 的框架,左图为单元的 LEF 文件,右图为工艺文件的 LEF 文件。

将制作完成的 LEF 文件导入 Milkyway 工具,建立单元的库文件。通过 Library>Dump Tech File 选项导出单元库文件上包含的工艺文件信息导出,在后续的设计中使用。

通过 Milkyway 工具导出的工艺文件格式与 SMIC 公司所提供的 Cadence 工艺文件在格式上的对比如图 4-18,左图为 Cadence 工具下的工艺文件格式,右图为 Synopsys 工具下的工艺文件格式。

2)库文件的设置

在提取工艺文件过程中,导入了版图的库文件,此时还需对物理库的设计进行一些参数的设置,对标准单元的特征进行标记。物理库的参数设置流程如图 4-19。

4.3.5 标准单元时序库的其他文件的生成

1)TLU+文件的生成

TLU+ 文件是提供互联线间的 RC 模型的文件,文件可通过 ITF(Interconnect Technology Format)进行转换。

ITF 文件则是提供互联线的寄生效应模型,为设计者进行时序、信号完整性和功耗等的分析提供精确的寄生参数。此文件一般由工艺厂商提供。

ITF 转换为 TLU+文件的方法是通过 Synopsys 工具下的 Star-RC 工具,使用工具中的命令行 grdgenxo -itf2TLUPlus -i -o 进行文件的转换。

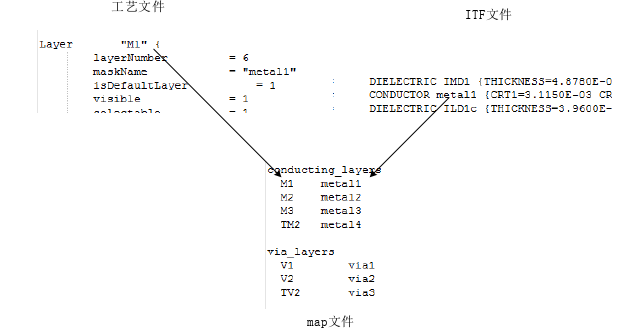

2 )映射文件(.map)的编写

由于工艺文件(.tf 文件)和 RC 模型文件(.itf 文件)可能来自不同的厂商,金属层与通孔的定义可能不一致。需要通过映射文件将工艺文件与 RC 模型对应起来。映射文件的编写格式如图 4-25。通过工艺文件与 ITF 文件中描述相同的层对应起来,建立一个映射的关系。

第五节 0.6V 55nm近阈值标准单元库设计

4.2.1 时序库文件

标准单元库时序库文件是数字电路设计逻辑综合和物理设计过程中进行时序分析必须要用到的文件,同时数字电路设计中时序分析的准确程度取决于时序库文件的准确性,因此精准的时序库文件是数字电路设计成功的重要保障。

时序文件的结构如图 4.3 所示,主要包括时序库文件环境、属性描述和各库单元的具体信息两大部分内容。其中库文件环境、属性描述主要包括以下内容:库文件的名称、版本等文件信息,库文件中的 PVT(工艺角、电源电压、应用温度)信息,库文件中使用数据及其单位信息、数据测量标准信息,以及查找表模板信息;而库单元的具体信息是时序库文件的主要内容,根据单元名称和驱动能力顺序排列,主要包括每个库单元的面积、Pin 角、功能、功耗(包括静态功耗和动态功耗)、时序以及时序弧信息,其中时序和功耗信息根据不同的时序弧以查找表的形式表征,当数字电路设计过程中进行时序分析时,EDA 工具根据查找表和非线性延时模型就能得到单元的当前使用环境下的时序信息,下面将对查找表和非线性延时模型进行具体介绍。

典型的查找表构成如图 4.4 所示,根据查找表的索引值——单元输入信号转换延时情况和单元负载电容情况,可以查找到单元部分工作环境下的延时情况,查找表中的时序数据的来源于单元带寄生参数的 Hspice 仿真,结果非常接近实际值。

非线性延时模型(Nonlinear Delay Model,NLDM)是时序计算精度较高的一种延时计算模型,也是目前工业界主要使用的一种模型[36]。该延时模型由输入信号转换时间与输出负载作为索引,若单元的工作环境恰好是查找表中的点,则可按索引值直接查到,若单元的工作环境不是查找表中的点,则跟据单元工作环境中的输入信号转换延时情况和输出负载情况,分别确定他们在查找表索引值中两个最临近的值,并找到查找表中对应的四个点,这四个点确定一个平面,根据这个平面的方程和单元当前工作环境中的输入信号转换延时情况和输出负载情况计算取得的结果,作为单元的延时结果。

通过上述非线性延时模型和查找表的介绍可知,查找表的边界和规模对单元延时结果的准确性有较大的影响,查找表中的值越多,则延时结果越准确。结合第二章中近阈值电压对单元特性的影响,本次设计中,通过分析实际使用时单元可能出现的输入信号转换延时情况和负载电容情况,重新界定了近阈值电压下二查找表两个索引值的边界,并通过相对误差统计分析,将商用单元库中 7×7 的查找表规模扩展为 20×20 的查找表规模,有效提高了近阈值电压下单元延时结果的准确性,也就提高了近阈值电压下时序库文件的准确性。

4.2.2 建库流程

本次设计采用 Siliconsmart 工具进行标准单元的特征化建库[49],主要包括如图 4.5 所示的一些步骤。

其中数据准备主要指准备带寄生参数信息的库单元网表、工艺厂商提供的仿真模型文件以及作为结构模板的商用标准单元库时序库文件;配置参数文件主要指配置带寄生参数的网表和在 configure 文件中设置需要的 PVT 环境、仿真模型、测量标准等参数信息。

Siliconsmart文件准备

电路网表.cdl

CIW->File->Export->CDL

模型文件.l

仿真网表格式主要有两种:Spice格式及Specte格式,两者不能通用,但是Spectre提供了Spice格式Model转Spectre格式Model的工具:

spp -convert <input.sp> output.l这个在model文件里面,各个PDK文件夹下面有一个spice model名字或直接名字就是model的文件,里面有关于工艺库各种器件的spice model参数或器件的spcie,verilogA描述。不同的fab厂的文件组织结构并不一样。有的PDK,比如TMSC的数据都在一个后缀为.scs位文件里面,里面除了定义了spice model参数,还定义了subckt,有的器件在电路图中引用的是相关的subckt。model和subckt就是关键字,后面的数据就是相关的参数和或表达式。另外还定义了工艺角,也就是tt,ss,ff…这些。工艺角的关键字为section。你要找的spcie model数据都在model关键字开头的段落。SMIC的PDK组织结构一般主要包含,lib, mdl,ckt三种后缀的文件,lib定义工艺角,mdl定义model,ckt定义subckt。引用自《smic018工艺中nmos管 uncox 值一般取多少?》

时序模板.lib

参考文页之前的模板描述:

亚阈值数字标准单元库的设计3.2.2时序库的建立

模板文件(template)的内容可以分为两部分:整个库的模板和单元的模板。整个库的模板定义了时序库文件中的一些全局参数,如单元上升、下降时间、单元延时的定义及具体测试方式,库中最大、最小转换时间及最大负载电容等。单元的模板则是定义了每个单元相关的参数,包含单元的输入、输出端口定义,延时、时序约束和功耗的查找表模板等。如图 3-7 所示,是一个只包含两个单元的库模板文件。模板文件需要手写得到,当单元数目较多时工作量较大。当只是对原有库中的单元进行重新特征化时,可以直接利用特征化工具从原有的库中提取出模板文件,然后对模板中的部分内容进行修改即可。

【SiliconSmart基础篇】了解基本文件及命令(中)

Sequential Cells

对于标准时序单元,您可以从 Liberty文件导入功能(Function)或使用走Functional Recognition流程来提取function。 对于更复杂的时序单元(例如retention logic cells),SiliconSmart 工具更难识别出单元功能的细微差别。 在这种情况下,最好先将必要的信息添加到单元实例文件(cell instance files)中,并且在使用任何标准 TCL 函数都无法表达复杂功能的时候,使用 add_user_stimulus进行辅助。《Siliconsmart ACE User Guide》p75。

SiliconSmart 提供了两种方法来描述时序单元:1.用add_flop 和 add_latch 命令描述标准触发器和锁存器,以及2用add_talbe命令指定复杂电路的状态表。