1.Pipeline ADC校准

高速高精度流水线ADC是模拟集成电路的重要组成部分。由于制造工艺的原因,ADC中的采样电容宗师存在不匹配的问题,采样电容的不匹配会造成ADC的线性度变差,在频谱上表现为无杂散动态范围(SFDR,Spurious Free Dynamic range)变差。

调高SFDR的校准方法有动态电容匹配技术(DEM,dynamic element matching)技术,抖动注入(dither injection)技术。虽然它们都有较好的提高SFDR的效果,但是DEM技术会导致信噪比(SNR,signal noise ratio)变差,也就是说DEM技术是以牺牲SNR为代价,来提高SFDR。抖动注入技术需要注入一个随机信号,使得输入信号的幅度受限,牺牲了输入信号的幅度范围。【1】

2.自热补偿和衬底温度补偿

2伞状结构吸热

假设探测单元为10um,黑体面源边长为10cm,黑体辐射功率为10mW,帧频为60Hz。吸收率为17%。已知钛的比热 (C) 是 0,532 千焦/(公斤·ķ)。钛伞的质量=体积*密度。体积是伞面的体积10um*10um*5nm+墩子的体积pi*10um*2um*2um,钛的密度密度为4.506g/cm 3。则钛伞的温升为:

(10^-2*10^-8)*(1/60)*0.17/(532)/((10^-8*5*10^-7+10^-4*4*10^-8)*4.5/1000)=0.0296K

此计算结果没有考虑氮化硅,氮化硅的比热容0.71J/(g·K)。

3.IP核面积汇总

1.10位流水线ADC SMIC 0. 25μm工艺,面积仅为 0. 24mm2

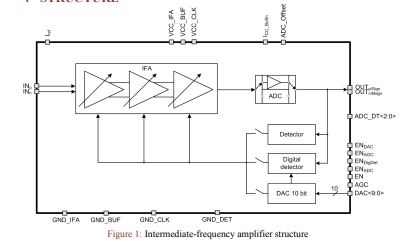

3.中频放大器Intermediate-frequency amplifier 0.5 mm2

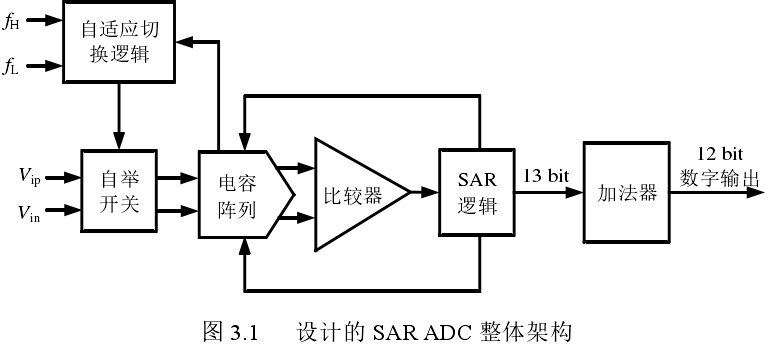

4. 12bit SAR ADC .18工艺

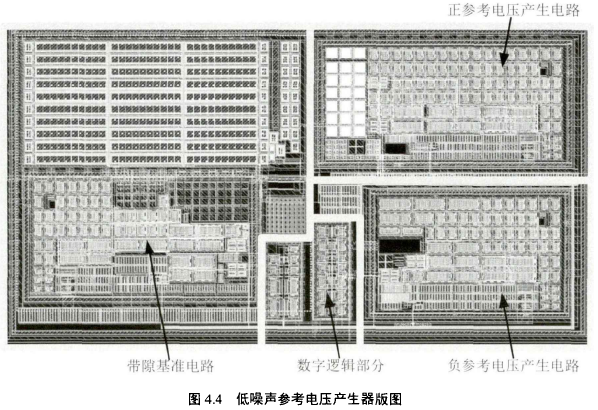

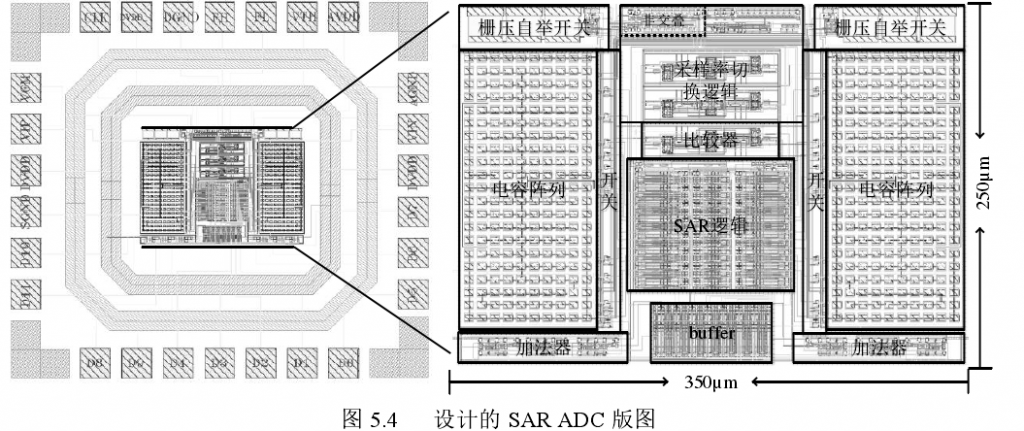

本文设计的12bit SAR ADC中的低噪声参考电压产生器电路和SAR ADC主体电路分两次流片,各自测试后根据测试结果修改版图再联合流片。

低噪声参考电压产生器电路整体版图及内部各个模块如图4.4所示,版图尺寸为1720um*944um。

12bit SAR ADC整体版图及内部各模块布局如图4.5所示,版图尺寸为2597um*2134um。

4.模拟版图知识点汇总

4.1 Slot 的作用:

1.使电流的分布比较均匀(因为电流有趋肤效应即“集边效应”,属上的电流分布可能都在边上,而不是均匀分布在金属上的)

另外,用slot可以比较好的引导电流的流动方向,在有拐角的地方,使电流不至于都聚集在拐角而导致发热.

2.同样时金属的分布比较均匀.(太大片的金属在做刻蚀的时候的刻蚀率是跟小块金属不一样的,slot提高了金属分布的均匀性,在各个位置DIE 的METAL 刻蚀之间保持比较平衡,提高yield)

3.使芯片有比较均匀的散热。

4.金属传导电流时会发热,就会导致膨胀。如果是一大片金属的话就会有鼓起变形的现象从而影响到芯片,用slot 的话就可以防止这种现象。可以提高芯片良率以及可靠性,防止老化过快。

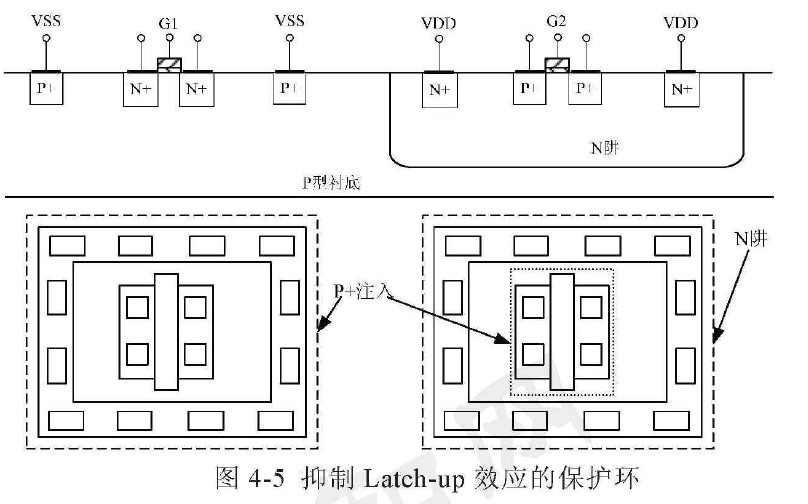

保护环应广泛应用于SAR ADC等模数混合电路,敏感的模拟电路和数字电路分别放置各自的保护环。对于模拟电路,PMOS放置的保护环接至模拟电源,NMOS的保护环接至模拟地;而对于数字电路则分别接至数字电源和数字地,以减小数字电路的噪声。

4.2关于 metal 覆盖率的解释:

- 太高会造成等离子etch 的时候容易放电,如果覆盖不均匀会造成等离子体密度不均匀,etch速度不均匀

- 覆盖不够就不能有很好的CMP Local 平整度(这里可以指Al 工艺里Interal MetalDielectric CMP,也可以是Cu 工艺里CuCMP),但在讲覆盖率时还要注意pattern 尽量均匀分布. 通常layout 之后要加dummay 以满足金属覆盖率

- 覆盖率适中可以大大提高产品可靠性。

4.3噪声的问题

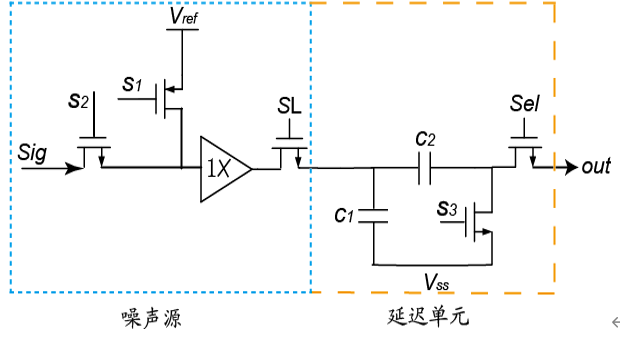

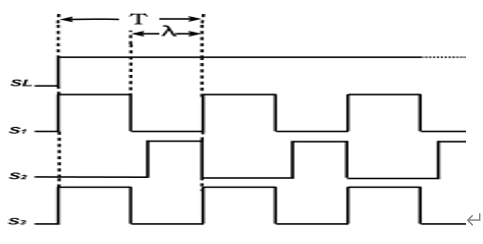

本文所描述的噪声现象不是由于热噪声或者电荷散射所引起的,而是由于CMOS I/O 驱动器的输出管脚上的电平变化,在电源总线(VDD 和VSS)上产生的噪声电压所引起的,被称为电源总线噪声(power bus noise)。

我们知道,每当CMOS 门改变其输出电平时有一个电流尖峰(current spike)流过电源总线并产生噪声电压,称它是开关噪声。电源总线以及它们与封装管脚的连接必须有足够的导通性能,使得来自输出驱动器中的所有电流尖峰不致于产生过大的噪声电压,破坏电路的正常操作。然而,芯片中的电源总线以及压焊封装连接线都具有电阻和电感特性,在多个I/O 驱动器(或者输出驱动器)排列的版图区域内,最有可能在电源总线上产生较大的噪声电压,过高的电源噪声电压还影响电路的延迟时间,使电路可能出现迟滞故障。为了保证电路安全可靠地操作,需要减小和限制电源总线噪声。下面从版图设计角度来考虑如何进行好的强壮的电源设计。

从结构和布局考虑

所谓 VLSI 结构式布局(structuring place-ment)是首先确定功能单元(例如:数据通道、控制模块、存贮器、随机逻辑等)在芯片上放置的区域,然后再分配I/O 驱动器及压焊点的位置。当功能块确定了所在区域后,就意味着确定了电源线(VDD)、地线(VSS)和时钟线的分配区域。

因为在I/O 区域内产生电源噪声最大,所以将它们组成在一起采用与其它功能单元相分离的电源总线,并称为“噪声”电源总线(noise power bus);而功能单元区域中的电源总线称为“静态”电源总线(Quiet power bus)。输入缓冲器上的电源总线可以由“静态”电源总线来提供。这两种电源总线采用各自的压焊点连接不同的管脚,实现电源总线噪声的区域隔离。根据I/O 驱动器的数量和输出驱动电流的大小,“噪声”电源总线可以有多个压焊点及连接管脚。压焊点的位置往往放在距封装管脚最近处,减小连接线的长度。

输出驱动器及分配

为了减小每个输出驱动器在输出电平变化时流入电源总线上的电流尖峰,在驱动器与电源总线连接通道上加入噪声限制电阻,这对大电流驱动是非常必要的。此外,就是对每一个VDD 和VSS管脚分配一组输出驱动器。每一个VSS 和VDD 所分配的输出驱动器组的数目是有限制的。在两个VSS(或者VDD)之间所分配的输出驱动器为一个VSS组(或者VDD组)。每一个VSS组(或者VDD 组)输出驱动器的数目是由输出驱动器类型(是否有噪声限制)和驱动电流确定,这在VLSI 版图设计时必须要充分考虑。

另外,如果在版图上有不闭的电源总线,电源总线的末端又远离VSS 和VDD 管脚,那么在该处电源噪声最大,因为电源总线本身的电感和电阻正比于电源总线的长度,对电源总线进行充放电的CMOS 门数也正比于电源总线的长度,所以电源总线上的噪声电压正比于电源总线长度的平方。因此,输出驱动器尽可能地分配在靠近每一个VSS 管脚。

总之,电源总线噪声问题是VLSI 设计者在版图设计时必须给予充分考虑,特别要注意输出驱动器同时开关噪声。在CMOS 数/模混合电路中,电源总线噪声影响程度比纯数字CMOS 电路更严重。通过VLSI 版图设计技巧、分离“静态”和“噪声”电源总线、增加VSS 和VDD 管脚数量及噪声限制输出驱动器等方法,控制电源总线噪声,使VLSI 芯片能安全可靠地操作。而且,事实上,对于噪声的抑制除了电路设计上要进行充分的考虑和采用不同的手段使信号足够干净之外,版图设计者拥有一定的电路设计知识和基础理论,养成一个良好的设计习惯(比如在大电流的地方习惯于尽可能多的VIA-stack 和对衬底接触,对于如何隔离不同的干扰源和噪声,如何有效的采用一些简单直接的版图设计技巧并且自然的应用到设计当中)对于整个设计在最后物理实现中避免未知因素导致的失效,将非常非常重要

噪声和 MOS 管的L×W 是成反比的,就是说,L×W 越大(面积越大),噪声越小。所以在精确的模拟线路中,你可以发现 OP AMP 的输入管的尺寸都做的很大。

【博士创芯说ISSCC2022一篇文章ring-amp+KT/C噪声消除技术-哔哩哔哩】 https://b23.tv/YSzbHre ring-amp, KT/C noise concellation

ISSCC 2021: Sony 50.1MP Full-Frame Sensor with Sigma-Delta ADC and kTC Noise Reduction

4.4分离走 VDD,GND 的走法

注:bipolar,Cmos 的不同方式

ESD 需要瞬间释放很大的电流,要求接触电阻尽量的小,因而contact 要求比较大。

随着器件尺寸的缩小,结深一般比较浅,如果开孔比较大,在淀积金属时容易透过源漏直接与衬底相连,因而孔不能太大。

4.5关于 guardring 得加法

如果隔离部分主要为N 型器件,则Gnd 在里面,VDD 在外面;如果隔离部分主要为P 型器件,则VDD 在里面,Gnd 在外面;如果隔离部分P、N 差不多,若是P-sub,则Gnd 在里面,VDD在外面,这样VDD 可以起到隔离胡作用。

JFET 栅上加poly 的作用是为了防止光电流对JFET 的影响。因为在wafer 测试的时候会有光照到要测试的DIE 上的。

4.6 设计PCB和画IC版图哪个更难?更需要技术?

作者:知乎用户

链接:https://www.zhihu.com/question/48432503/answer/112715278

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

我觉得这两者并不能很简单的比较,IC layout engineer可以很厉害(什么都懂一点,很有全局观,哪些东西应该放哪里等等,很会把握project的进度,有前瞻性…通常这些人会慢慢升上去做layout lead -> manager,等等);也可以不用懂很多,譬如我们公司的有些layout engineer其实完全没有电路背景的,知其然不知其所以然,所有经常会有时候不太make sense,不过画的很快,凭经验和手速也可以一直干下去(画完我们都要review,designer不满意就要按照designer改,他们可能就一直会在画block level了…)。画得很好的,处处都很讲究,该matching的地方matching, shielding的地方shielding,sensitive的地方很注意整个环境的一致性,不会范低级错误,等等,画得不好的…lvs和drc clean就觉得好然后不断让designer review,再改,或者到后面干脆designer自己来改…

上面提到rule很多很复杂的问题,我觉得现在有这么多方便的tool,rule又不用记,debug很方便,熟练了其实都不是什么问题。再有关于复杂度,一整个看固然很复杂眼花缭乱让人不明觉厉,但是都是一个个block搭起来的,一个个clear了drc,lvs等等,而且大芯片有很多个layout engineers一起做出来,分工起来其实并没有很复杂。关于后仿,一般都是designer跑的,因为某些电路对某些parasitic可能比较敏感,所以layout会影响performance,画得不好的layout会导致各种问题,coupling, rc delay/timing, latch-up, EM(electromigration, 电子迁移?), etc. 我觉得要求高的pcb也有各种各样问题,感觉是一样的,需要注意的地方不同罢了。

所以我觉得这两者大致同等的。画pcb layout的一下子肯定不能画IC layout, 画IC layout的你让他去画pcb一下子也画不出来。不过话说回来,这两者的门槛都不算高,给一段不长的时间training就可以上手,譬如画IC layout的训练一段时间去画pcb layout估计也是可以的…

上面有人提到设计,这两者确实不太一样,譬如Analog IC designer可以画layout,而且可以画得很好,因为知其然知其所以然,虽然速度可能比不上专门画layout的熟练工,(大部分designer)也可以画pcb layout,但是反过来就不行了。门槛不一样导致工资不一样可以理解的。

4.7 集成电路中闩锁效应的小结

这里把 CMOS 中的闩锁效应(latch-up)的来源和一些具体的避免 latch-up 的方法的内容做一些小结.

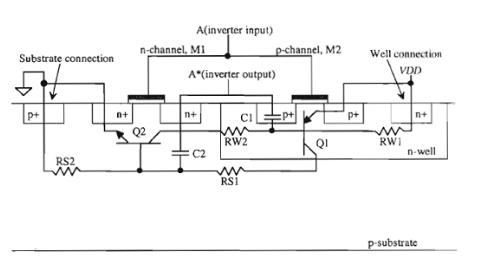

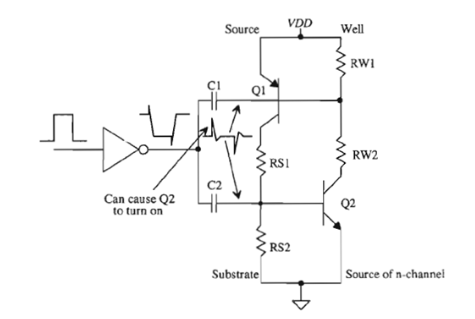

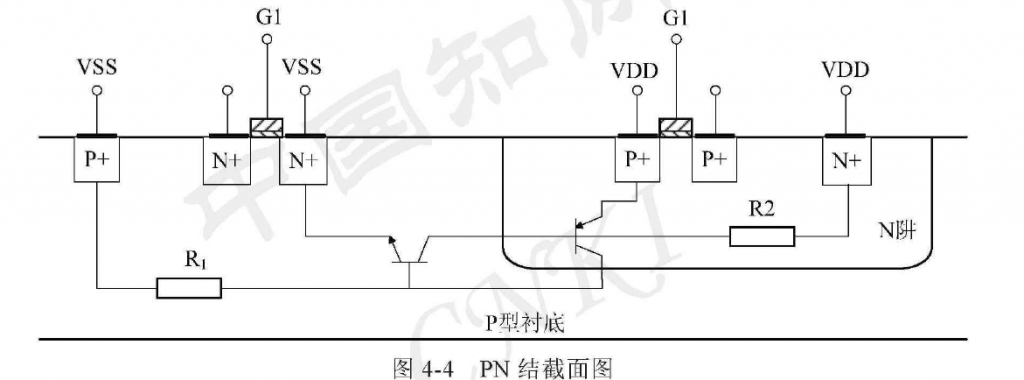

CMOS 中的 latch-up 问题来源于其寄生的 NPN 与 PNP 双极晶体管形成的 PNPN 结构, 具体的闩锁效应产生原理的分析,可以以一对反相器为例(如下图中所示)来说明。

图中 inverter 的 PMOS M2 在阱内形成的纵向双极型晶体管 PNP,NMOS M1 在衬底上形成的横向双极晶体管 NPN,这两个双极晶体管接成一对,可以看到反偏的阱-衬底结是两个晶体管的集电极。

产生 latch-up 的具体原因:

- 芯片一开始工作时 VDD 变化导致 Nwell 和 P-substrate 间寄生电容中产生足够的电流,当 VDD变化率大到一定地步,将会引起 Latch up。

- 当 I/O 的信号变化超出 VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致 SCR(silicon-controlled rectifier)的触发。

- ESD 静电加压,可能会从保护电路中引入少量载流子到 well 或 substrate 中,也会引起 SCR 的触发。

- 当很多的驱动器同时动作,负载过大使 power 和 gnd 突然变化,也有可能打开 SCR 的一个 BJT。

- Well 侧面漏电流过大

如何防止 latch-up,具体的方法:

- 在 substrate 上改变金属的掺杂,降低 BJT 的增益

- 避免 source 和 drain 的正向偏压

- 工艺上,在重掺杂的衬底上增加一个轻掺杂的 layer,阻止侧面电流从垂直 BJT 到低阻衬底上的通路

- 使用保护环 Guard-ring: P+ ring 环绕 nmos 并接 GND;N+ ring 环绕 pmos 并接 VDD,一方面可以降低 Rwell 和 Rsub 的阻值,另一方面可阻止载流子到达 BJT 的基极。如果可能,可再增加两圈 ring。

- Substrate contact 和 well contact 应尽量靠近 source 端,以降低 Rwell 和 Rsub 的阻值。

- 使 nmos 尽量靠近 GND, pmos 尽量靠近 VDD, 保持足够的距离在 pmos 和 nmos 之间以降低引发 SCR 的可能

- 除在 I/O 处需采取防 Latch-up 的措施外, 凡接 I/O 的内部 mos 也应圈保护环 guard ring

- I/O 处尽量不使用 pmos (nwell)

5.模拟噪声仿真问题汇总

Spectre Noise 仿真求助:Noise Summary中器件名后面的fn、id等参数代表什么意思?

cadence 噪声仿真问题: equivalent input noise VS. noise summery 仿真结果不同

Spectre进行transient noise仿真,如何查看仿真结果?

In transient analysis, lower limit of the time step is implicitly influenced by the circuit bandwidth.

When the circuit is latent, or signals are changing slowly, the simulator takes larger steps to go faster

without compromising accuracy. During transient noise analysis, the time step is limited by the noise

bandwidth. Since noise sources are always active and are updated with constant time interval, time step

becomes uniform. Therefore, transient noise analysis for circuits with long periods of latency will be

significantly slower than normal transient analysis. For performance reasons, it does not make sense

to set noise bandwidth much higher than the circuit bandwidth.

回答下你的第二个问题吧,关于管子W、L、veff的选择,现在比较流行的是用反型系数配合gm/ID法找到最佳的tradeoff和optimization。反型系数提供归一化模型,gm/ID找到比较贴近的计算数值。

具体的操作方法比较复杂,你可以看看《A CAD Methodology for Optimizing Transistor Sizing in Analog Design》,《A gm/ID Based Methodology for the Design of CMOS Analog Circuits and Its Application to the Synthesis of a Silicon-on-Insulator Micropower OTA》以及他们所引用的论文。

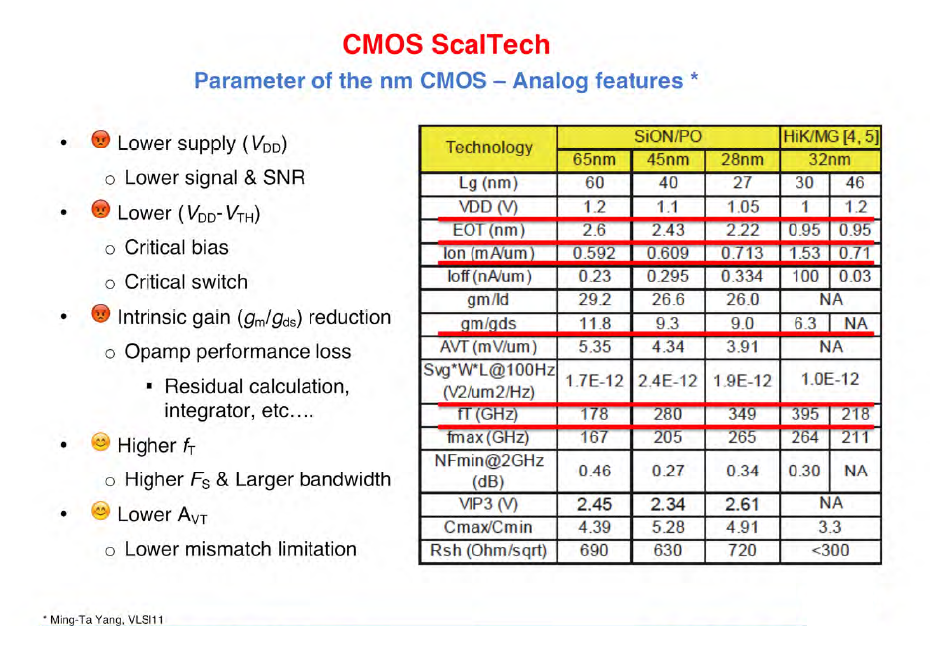

这些方法对理论的要求比较大,尤其是管子器件的物理性能。最近学习LNA设计,45nm仿真出的单个管子的曲线已经完全和长沟道不一样了,看了thomas lee教授(2000年左右)还有razavi等相关文章,虽然理论可以看差不多明白,但是一到仿真软件,真不知道如何将上述大牛的理论和当今小尺寸的器件模型结合起来,平时工作很忙,这些都是业余充电,希望尽快看些相关文章并有所收获。

不客气,平方率公式虽然对电路设计有很好的指导性,但是对于如今的短沟道器件已经无法得出哪怕相近的值。Binkley、Boris、Silveira、Jespers这些大牛们给出了行之有效的解决思路。可以多看看他们的论文,如果能和实战结合,那就真的能让自己的设计能力提升到一个新的层次了

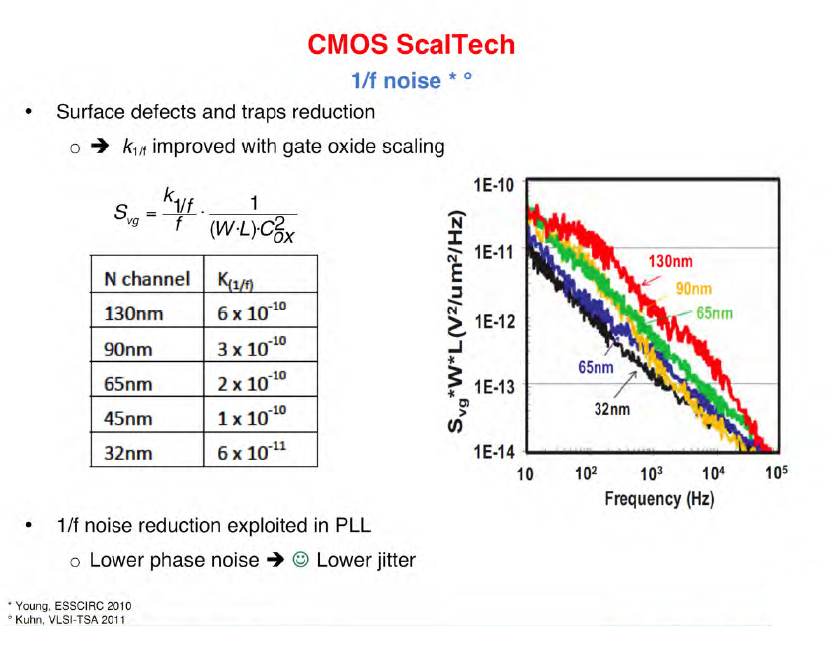

mosfet 三种噪声仿真报告 (CMOS Process Transient Noise Simulation Analysis and Benchmarking,此论文有点重要)

In order to examine the validity of all three dominant noise sources in terms of the transient noise analysis results, three separate test-benches were implemented, as shown in Fig.3. In all three topologies an RF device with a total width of W = 32 ?m, and length of L = 65 nm was used. AC noise versus transient noise simulations were performed in a 65 nm RF CMOS process commercially available by TSMC.

AC noise can simulate accurately the frequency dependence of gate noise while the transient noise cannot. This is because

SPECTRE noise analysis has restrictions.

For an independent source the spectral density function provided or given within a noise file (if this type of noise source is used), should be decreasing with frequency and since this is not the case of gate induced noise and therefore this noise source is not compatible with transient noise, resulting in inaccurate results.

The correct model approach is to have a physical white noise source, and to achieve the frequency behavior by a high pass transfer function.

This was implemented in schematic level into the Virtuoso suite with a white noise source and an CR high pass filter. The transient noise spectral density versus the AC noise spectrum is provided in Fig. 5. Transient noise matches AC noise results and both analyses provide correct representation of gate noise. Therefore the demonstrated simulator limitation on noise sources that increase with frequency can be faced by implementing suitably white noise sources and a high pass transfer function characteristic.

6.SAR ADC中比较器的噪声仿真

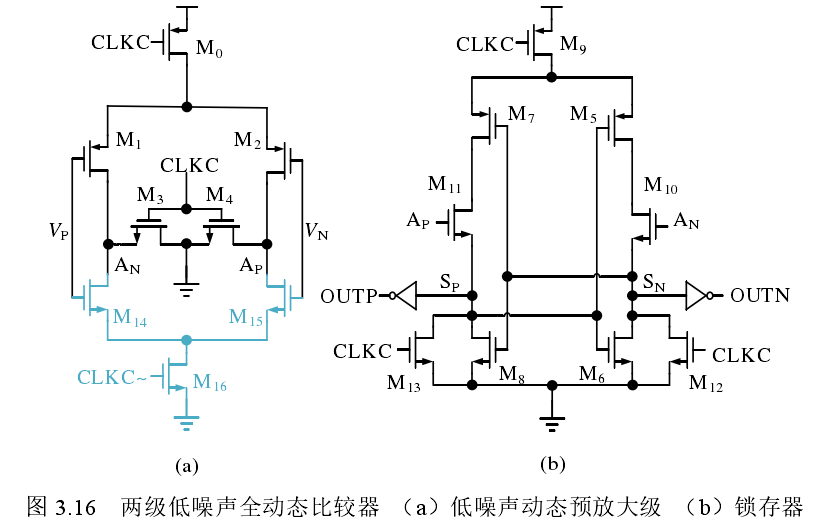

6.1 《具有自适应采样率的低功耗SAR_ADC研究与设计》

等效输入噪声是比较器的另一个重要指标。不同于静态失调,比较器的噪声会发生变化,从而影响线性度和信噪比。比较器噪声的仿真方法也不同于运放,其仿真的原理基于概率分析,由于噪声幅值服从正态分布,当比较器输入电压大小不一样时,其高电平出现的概率也

应该服从正态分布。具体仿真方法为:首先固定比较器一端的输入电压为500m V,另一端输入电压从499m V到501m V,每隔0.1m V

比较一次;然后加入瞬态噪声并仿真1000次;最后统计一端输出为高电平的概率,并计算标准差。《具有自适应采样率的低功耗SAR_ADC研究与设计》

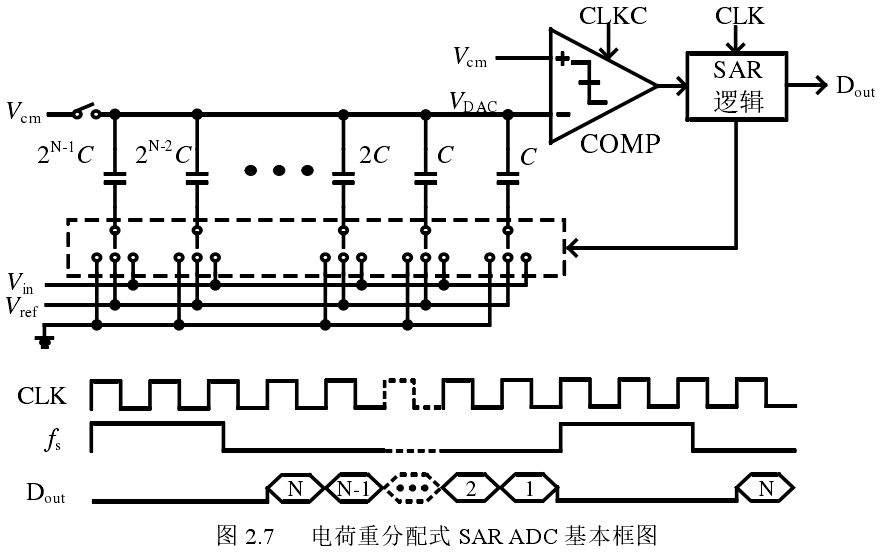

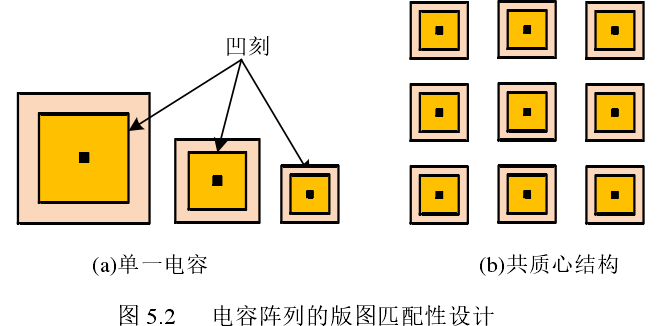

电容阵列的匹配性

对于电荷重分配式SAR ADC,电容阵列用于DAC。如图5.2(a)所示,由于掩模版的凹刻,电容存在失配。随着分辨率的增加,各电容之间的比例会和设计值产生误差,该误差进而影响线性度和有效位数。

一种常用的解决办法是采用单位电容,并以共质心结构排布[41-42],如图5.2(b)所示。这样凹刻以相同的方式影响每一个单位电容,且每个电容氧化层的一阶误差相等。但是该方法的缺点是会引起较大的寄生电容,需不断调整版图以达到性能要求。

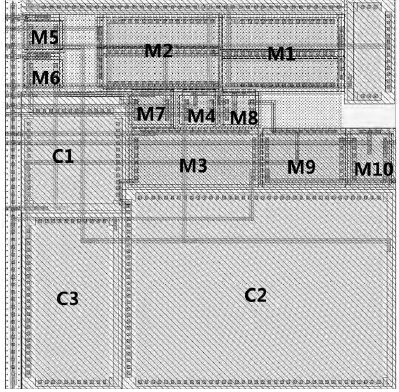

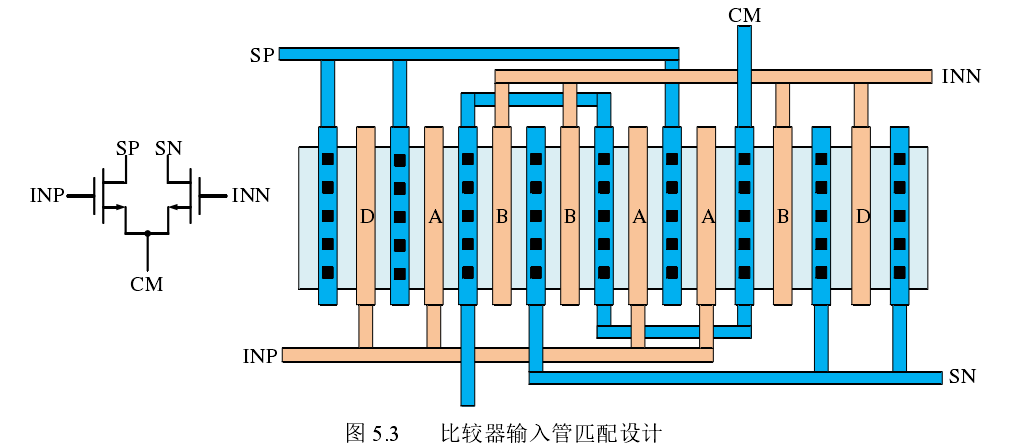

比较器版图的匹配性

比较器对器件的匹配性要求较高,尤其差分对管影响最大。差分对之间的不匹配会使得比较器两端的寄生电容不一致,从而引入动态失调,进而降低SAR ADC性能。在版图中提高匹配性的方法有:拆分为相同数目的finger;增加虚拟器件并接成MOS电容的方式,使匹配的器件受到相同的影响;需要匹配的器件尽量靠近等,如图5.3所示。

6.2ADC的DNL和INL《应用于高温MEMS加速度计的12bit SAR ADC设计与实现》

微分非线性

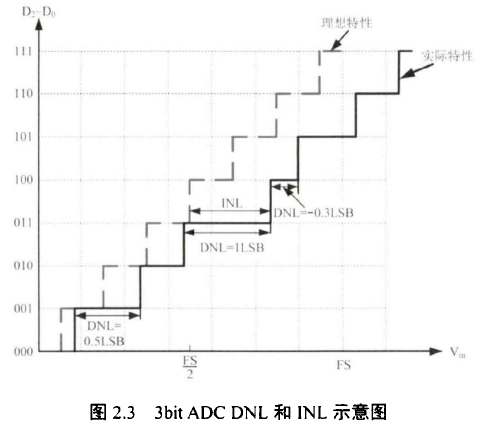

微分非线性(Differential Nonlinearity,简写DNL)是指ADC实际输入-输出特性曲线中相邻两个输出吗字之间对应的模拟输入电压差值与对应的理想输入-输出曲线中模拟输入电压差值的比值,通常以LSB为单位。一个3bit ADC的DNL示意图如图2.3所示。

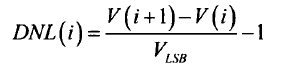

DNL的表达式为:

其中DNL(i)表示第i个量化区间的微分非线性,V(i+1)和V(i)表示第i+1个和第i个台阶对应的实际模拟输入电压值,VLSB表示ADC能分辨的最小模拟输入电压。

积分非线性

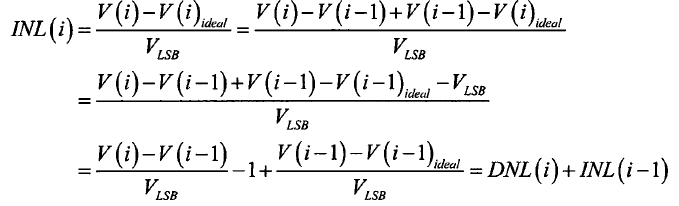

积分非线性(Intergral Nonlinearity,简写INL)是指ADC实际输出数字码字对应的模拟电压与理想模拟电压之间差值。一个3bit ADC的INL示意图如图2.3所示。INL的表达式为:

其中INL(i)和INL(i-1)表示第i个和第i-1个量化区间的积分非线性,DNL(i)表示第i个量化区间的微分非线性,V(i)和V(i-1)表示第i个和第i-1个台阶对应的实际模拟输入电压值,V(i)ideal和V(i-1)ideal表示第i个和第i-1个台阶对应的理想模拟输入电压值,VLSB表示ADC能分辨的最小模拟输入电压。

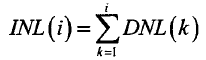

由于在第一个量化区间内INL(1)=DNL(1),结合式(2.3)逐步递归可以得到:

附加连接:

6.3 《高效模拟前端集成电路》第四章数据转换器,SAR ADC噪声:

(1)kT/C噪声:等效输入噪声与本级的精度M无关,而与采样电容值成反比。要使热噪声降低,只能提高采样电容;而提高采样电容,会使功耗增加。因此在设计时要在SNR和功耗之间折中。

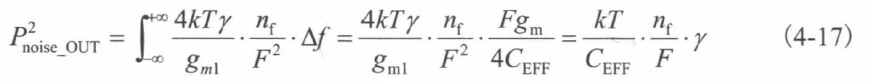

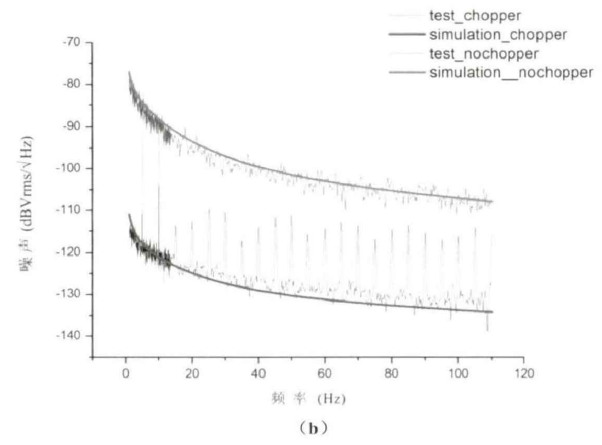

(2)运算放大器噪声:除了采样网络产生噪声外,运算放大器也会引入噪声。由于开关电容电路中不存在静态电流,且电路中管子的工作频率较高,闪烁噪声的影响可以忽略。输出端噪声功率为:

可以看出,由于存在热噪声,实际得到的SNR比理想的SNR小,所以单纯地从量化噪声的角度设计ADC时不合理的。电路设计者必须对量化噪声和系统热噪声进行合理分配。

6.4 斩波调制技术在SAR ADC中的应用测试结果,《应用于高温MEMS加速度计的12bit SAR ADC设计与实现》

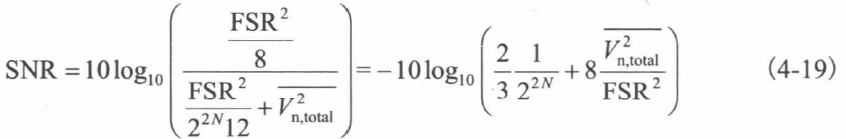

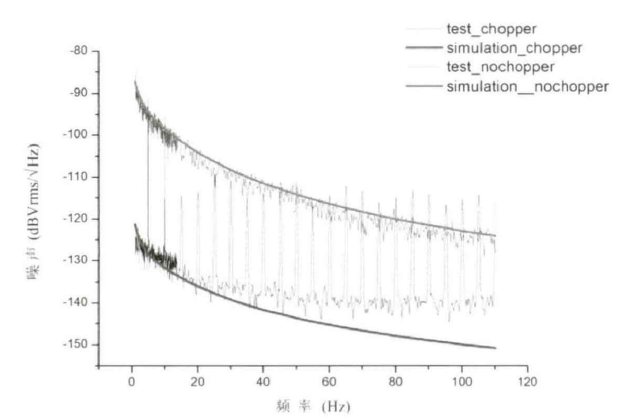

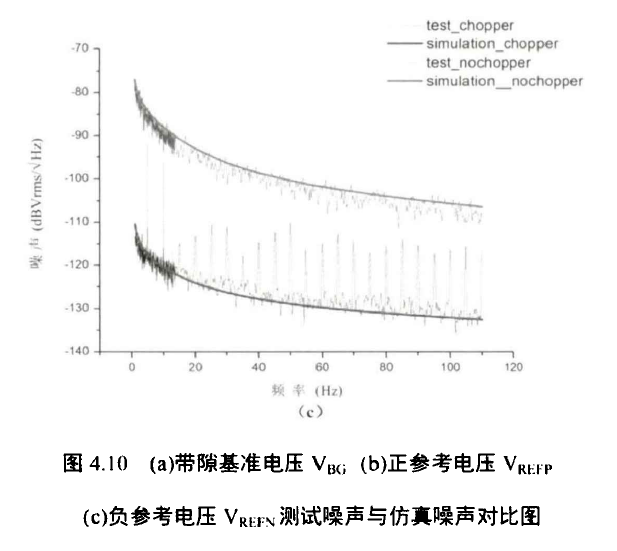

图4.10所示为低噪声参考电压产生器芯片的三个输出电压分别在有无斩波情况下的测试噪声曲线和仿真噪声曲线对比图。

Generation of 1/f noise using Matlab.

fv = linspace(0, 1, 20); % Normalised Frequencies

a = 1./(1 + fv*2); % Amplitudes Of ‘1/f’

b = firls(42, fv, a); % Filter Numerator Coefficients

figure(1)

freqz(b, 1, 2^17) % Filter Bode Plot

N = 1E+6;

ns = rand(1, N);

invfn = filtfilt(b, 1, ns); % Create ‘1/f’ Noise

figure(2)

plot([0:N-1], invfn) % Plot Noise In Time Domain

grid

FTn = fft(invfn-mean(invfn))/N; % Fourier Transform

figure(3)

plot([0:N/2], abs(FTn(1:N/2+1))*2) % Plot Fourier Transform Of Noise

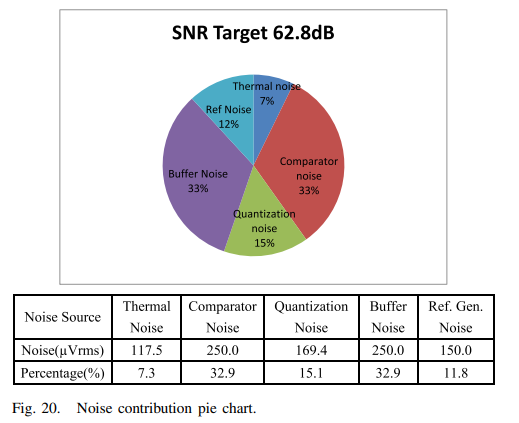

grid6.5 SAR ADC中不同部分噪声占比

7.晶体管级噪声优化技术

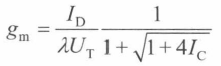

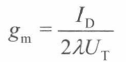

晶体管级噪声优化的主要方法是增大输入及跨导放大器的跨导gm,同时减小跨导放大器的噪声电流inoise。采用高电压供电、增大输入偏置电流、增大输入管尺寸等方法达到增大运算放大器输入跨导并减小噪声电流的效果,但会引起功耗和面积的显著增加。为了获得更优的电流跨导效率,可以通过优化跨导放大器中晶体管的偏置状态、增大有效跨导等方式在小电流下获得更高的跨导,从而达到优化噪声性能的效果。当跨导发达器的输入管处于亚阈值偏置状态时,其跨导gm可表示为

其中UT为热电势26mV,lamda为亚阈值斜率因子,IC为反型系数。当输入MOS管被偏置在深亚阈值区(IC约等于0)时,可获得的最大跨导为

剩下部分直接去书中获取

《高效模拟前端集成电路》朱樟明著,p66,

本书中还写了几种低功耗、高性能CMOS仪表放大器优化技术,分别是1.低电压电路实现技术2.晶体管级噪声优化技术3.输入有效跨导提升技术4.源极退化技术5.斩波调制技术

在本书的第六章:传感器前端接口电路,还介绍了低功耗斩波仪表放大器

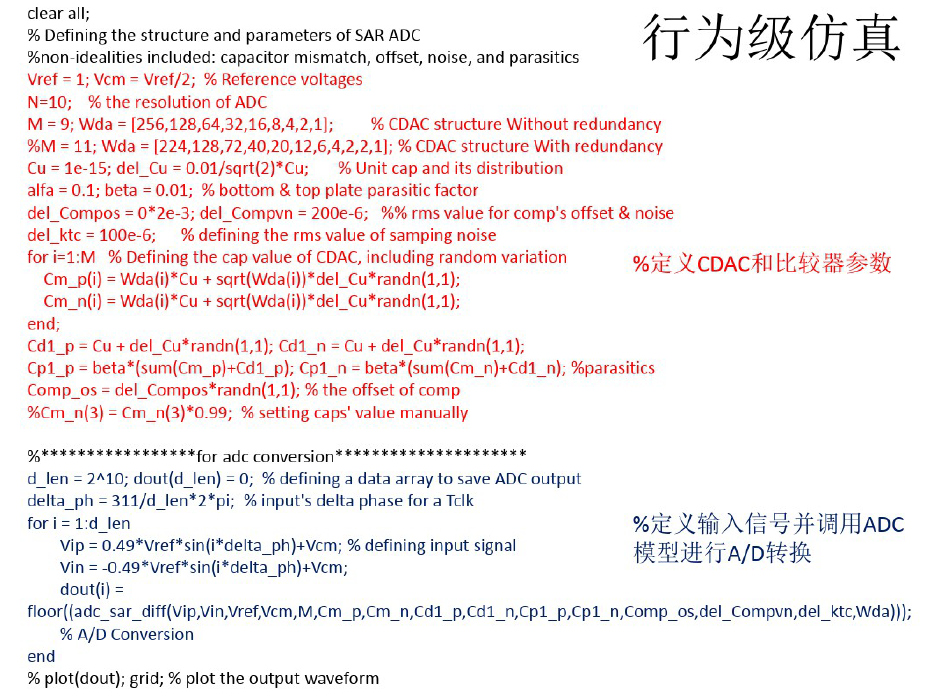

8.用matlab对ADC建模(各种ADC比较)

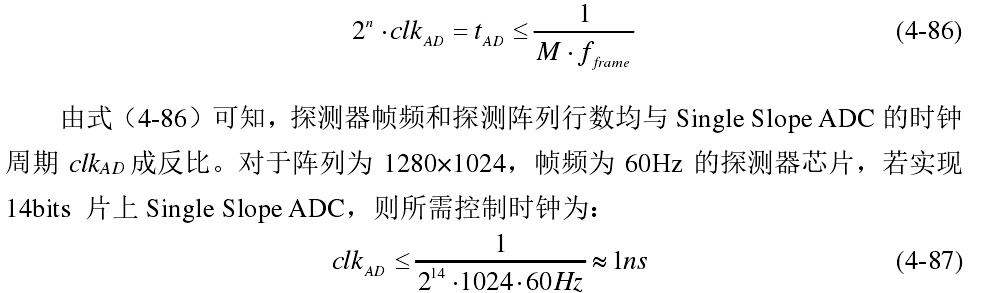

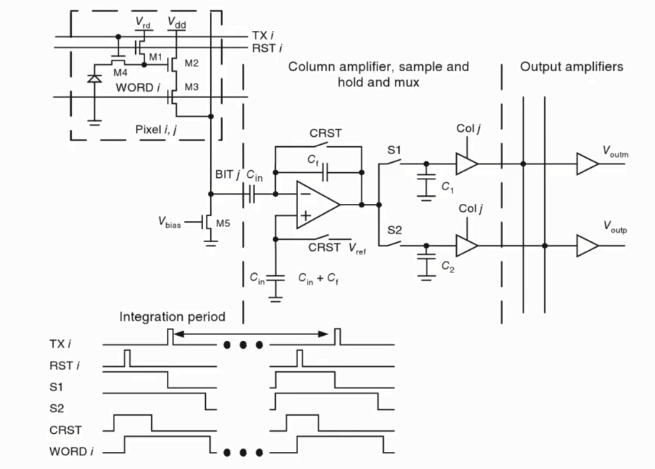

图像传感器中常用的列级ADC的种类又有很多,其结构特点、性能各不相同,可以满足不同应用场合的需求。常见的SAR-ADC精度可以达到很高,芯片功耗低,常采用电容阵列结构的DAC,在面积上有所欠缺;流水线型ADC追求高速、高精度,但是相应的有较大的芯片面积和整体功耗,而且还需要数字延迟校准,电路结构较为复杂;Flash ADC速度很快,但精度相对不高,其所需要的比较器数量随ADC的位

数指数增加。单斜ADC能够产生高精度、高线性度的斜坡信号,且模块少设计结构不复杂,功耗较低,在CMOS图像传感器读出电路中应用比较广泛,但是其最大的缺点就是转换速度慢,对于N位精度的ADC,对模拟信号进行一次模数转换往往需要2N个时钟周期,但是列级

ADC可以同时对所有列并行转换,所以对ADC的转换速度等性能要求不是很高。本论文在研究列级ADC各种结构在国内外发展现状的基

础上,经过分析并折中考虑设计一款高精度,低功耗且易调整的单斜结构ADC,满足列级ADC的应用需求。《应用于图像传感器的单斜式ADC的设计研究》

集成电路设计实践课程设计-SAR ADC 李福乐 清华大学微电子所

2012年,天津大学在研究列级ADC基础上,基于0.18 µm工艺设计了一个单斜和SAR相结合的两步式ADC,利用一个5位的DAC实现10

位的转换精度。先由单斜ADC实现5位粗量化,再由SAR进行剩余5位的细量化,并采用了误差校正设计,提高了精度,减小了芯片面积和功耗,有效位数为9位。《应用于图像传感器的单斜式ADC的设计研究——马仁超》

2010年,日本Muung Shin,Masayukilkebe等人采用0.25μm工艺设计了一款12位,工作速度390 KHz的两步单斜ADC,该ADC由9位单斜ADC和3位TDC组成,测试结果的DNL和INL都在0.45 LSB以内[14]。 《应用于图像传感器的单斜式ADC的设计研究——马仁超》

2014年,韩国东国大学Woongtaek Lim、Jongyoon Hwang等人采用0.13 μm工艺设计出14位、60 KHz两步单斜ADC,ADC引入新型的

4输入比较器,提高了分辨率,其采用列自校准技术减小固定模式噪声(FPN),测得的列FPN为0.38 LSB,每列的功耗仅在98 μW[15]。 《应用于图像传感器的单斜式ADC的设计研究——马仁超》

鉴于目前图像传感器对ADC性能要求的提高,以及芯片面积功耗最小化的发展趋势,本文旨在设计一款应用于图像传感器读出电路的列级

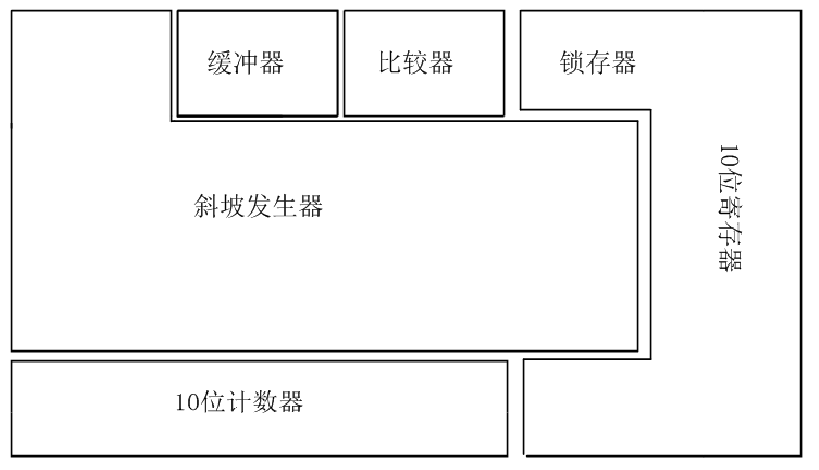

ADC芯片,由于列级ADC部分模块共用且多列并行转换的特点,使得芯片面积减小,并且对每列模数转换器的转换速度要求不高,又基于对精度和速度的需求,经过折中考虑后设计采用单斜结构的ADC,又鉴于对芯片面积的限制,本文将不采用电容阵列DAC的形式产生斜坡信号,而是应用了自适应斜率调整的开关电容积分电路构成斜坡发生器,以产生高精度高线性度并且受噪声影响小的斜坡信号,单斜ADC

核心的电路模块还包括斜坡输出缓冲器、具有失调电压消除功能的电压比较器以及数字码读出电路的数字模块,包括计数器、脉冲锁存器和寄存器等。设计基于0.13 μm CMOS工艺,经过初步计算和实际应用需求,确定ADC的性能指标,设计精度为10位,转换速度达到20 KHz

以上。根据设计指标和确定的电路架构,对各个模块的电路进行设计优化仿真,并通过观察仿真结果来验证设计的合理性。

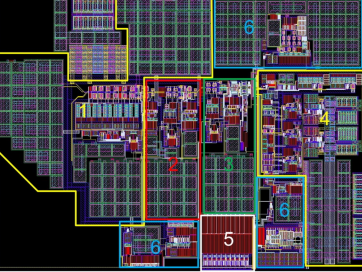

10位单斜ADC的版图设计

本设计单斜ADC的版图布局如图4.1所示,由于是数模混合信号电路,数字版图部分跟模拟版图部分要有隔离。并且模拟信号的抗干扰能力较弱,在布局时就要与数字模块分开。像是对精度要求较高的斜坡发生器模块,版图的走线就要绕开数字信号的走线,减少信号之间的串扰影响。另外对于版图的设计要注意器件的匹配性,因此在电路设计时就都采用了对称结构,保证了斜坡信号的线性度,减小了比较器的失

调电压。在设计中,为了减小数字部分的噪声对模拟部分产生影响,数字版图和模拟版图分别采用了各自的电源和地,在走线上优化布局,结构紧凑。 《应用于图像传感器的单斜式ADC的设计研究——马仁超》

9.斩波调制技术和自归零技术

9.1斩波调制技术

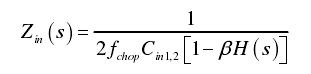

推导得电路等效输入阻抗为

9.2自调零技术

自调零(AutoZeroing,AZ)是一种离散时间采样技术,它的基本原理是在一个时钟周期对放大器输入失调进行采样,在另一个周期再将输入失调减去。如图36所示,自调零的基本结构包括输出失调存储(output offset storage,OOS)和输入失调存储(input offset storage,IOS)[76]。《低功耗生物信号采集前端研究_张三锋》

9.3亚阈值偏置

对于生物电信号采集,需要的带宽较小,仪表放大器的偏置电流通常在微安级,甚至是纳安级。低电流的工作状态通常使晶体管偏置在亚阈值区(弱反型区)。MOS管的亚阈值区指栅极电压VGS在阈值电压VTH以下,实际上,在这种条件下,栅氧化层界面处仍存在一个“弱”的反型层,并存在微弱的源漏电流,漏电流ID与VGS呈现指数关系,gm/ID表示单位电流可以提供的跨导大小,本质上表达了电流的跨导效率。

9.4电流复用

在采用亚阈值区偏置的基础上,文献[47,48,83]提出或改进了电流复用技术,进一步提高了电流效率。电流复用技术的基本原理是让同一个电流流经更多的提供输入跨导的单元。图3-15展示了电流复用的基本实现。如图3-15(a)所示,贡献输入跨导的只有NMOS输入对管,在图

3-15(b)中,NMOS和PMOS输入对管都贡献输入跨导。在亚阈值偏置条件下,假设所有管子有相同的gm/ID,因此N、PMOS互补的输入使得输入跨导在不额外消耗电流的基础上增加为原来的两倍,进一步提高了电流跨导效率。这里电流复用的代价是额外的尾电流源开支,因此降低了放大器的信号摆幅。

10.DC中slack为零?

在SDC文件中, 除了时钟的定义。 还会有 set_clock_uncertainty , 这个时间你自己定义, 一般都是ps级, 我个人常定义50ps,这个时间你可以算到你的时间余量里面,还教你一招, 在综合的时候, 你将时钟约束的占空比不要定义为50%。 以你的125M时钟来说, wavefrom {0 4}, 你可以将上升沿往前到3.5,如果以上升沿采样的话,时钟上升沿在3.5ns的时候都能正确采样,那真实时钟在4ns时钟也应该能采样, 查看综合的结果的时序违例,一般只在乎setup 是否违例,hold违例可以在后端去修正,综合后的时序仅供参考,前提是你要保证综合后setup不能有违例,至于slack为0可以放过,因为你在约束中有uncertainty时间的余量来保证的, 结果以你后端PT分析为准

要想确保电路能在流片后正常工作,通常会把时钟频率乘以一个倍率,给工艺流出余量,通常是加10%,比如你设计的电路工作频率为100M,那么综合的时候可以把时钟设为110M

11.LEF文件

LEF文件分为技术LEF和单元LEF。其中单元LEF又分为标准单元LEF和IP marco LEF。好像还有IO.LEF文件和ANT天线LEF文件。不知道I0.LEF和ANT天线LEF文件里的内容是什么?有什么作用?如果设计的PAD没有使用工艺库提供的,是不是就不需要IO.LEF以及io.lib文件了?

如果design 中有IO 并且是有timing 关系,如data input output PAd ,就需要有LEF and timing lib 。

如果IO 不需要在pr tool中处理,并且没有timing 要求,可以在virtuoso or laker 后端工具中添加。

LEF可以从gds 中提取,timing lib 可以仿真得到

我的设计由于是模数混合IC,数字部分是由APR产生版图,在数字版图里只对PIN进行了摆放(数字版图有的pin是直接作为芯片的输入输出端口,有的是与模拟模块连接),PAD和IO cell都是在virtuoso里由画版图人员完成的,因此在APR时没有用到IO.lef io.lib等库。 你说的“如果design 中有IO 并且是有timing 关系,如data input output PAd ,就需要有LEF and timing lib ”我不太理解,芯片肯定是有输入输出PAD的,不知道如何去判断design中是否有timing关系。如果没有用到IO.lef io.lib库,是不是用set_input_delay和set_output_delay来代替了IO cell的timing了呢?对于模数混合芯片,数字模块的PIN有的是直接作为芯片的输入输出端口的,有的pin是与模拟部分连接的,那么如果在数字APR时,怎么去用IO.LEF和io.lib库呢?还有PAD是不是只能用手工去画?SOC Encounter应该不能自动产生PAD吧。

LEF 文件是布局布线工具使用的cell 几何信息库的文件格式。布局布线工具将根据LEF 文件的信息决定怎样布局,怎样走线,怎样生成通孔等等。

一个cell 的完整版图包含了所有层的信息,但是在布局布线工具使用中,并不需要那么多的信息,布局布线工具只要知道pin 的位置、什么地方不能布线、等较少的信息就可以了,这样可以减少数据量,提高处理速度。有一些专门的工具用于将cell 的完整版图转成abstract,如cadence 的abstract generator。

The LEF format contains more than just the physical information contained in a GDSII or OASIS data stream, so many of the cell processing steps that must be done manually for a GDSII or OASIS library flow can be done automatically with LEF data. 《Library Data Preparation for IC Compiler User Guide》

12.流片相关帖子汇总

终于又流片啦

13.噪声系数相关

NOISE FIGURE MEASUREMENT METHODS AND FORMULAS

低噪放(LNA)噪声系数(NF)测试结果与后仿真结果偏差很大,什么原因???

运算放大器电路固有噪声的分析与测量 — 第二部分:运算放大器噪声介绍

MOS管衬底电位接法|PMOS、NMOS衬底连接-KIA MOS管

14. ADC 采样时钟抖动

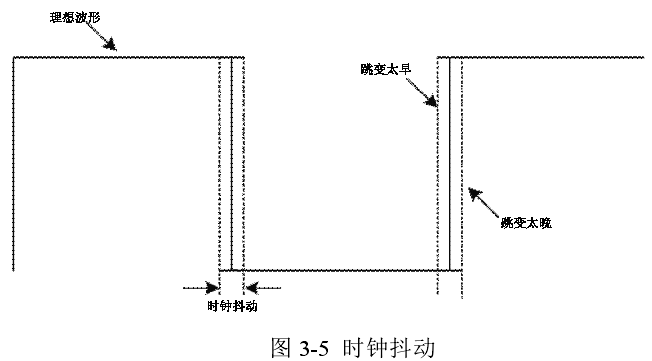

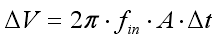

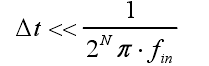

由于采样时钟周期T在受到电路系统中各种噪声因素的影响时,出现的微小的延迟或者超前,这种现象称为时钟抖动(jitter)[37]。其原因主要分为以下三种,一是由采保电路的噪声造成,二是由时钟发生器本身的相噪造成,三是由电源噪声引起。如图3-5所示。受此影响,采样输出电压产生一定的电压误差。

15. ADC量化噪声

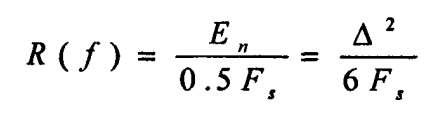

当输入为随机信号且幅度大于分层电平时,量化噪声在0~0.5Fs(Fs为采样频率)的频率范围内与频率无关,即它具有白噪声的性质,所以量化噪声的功率密度谱为:

16.Cadence中calculator的使用

17.Σ-△ ADC原理

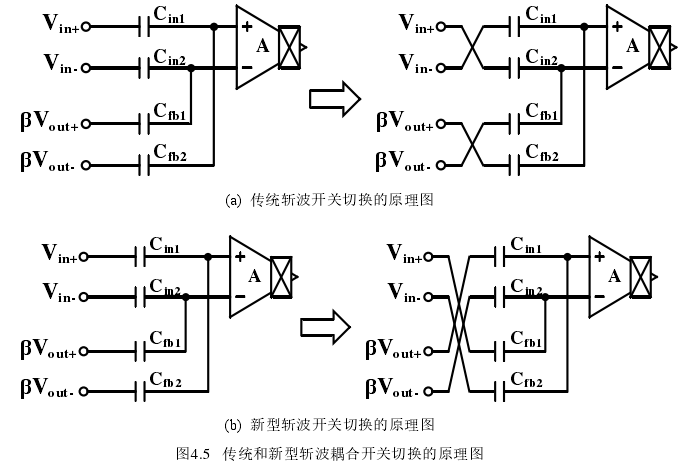

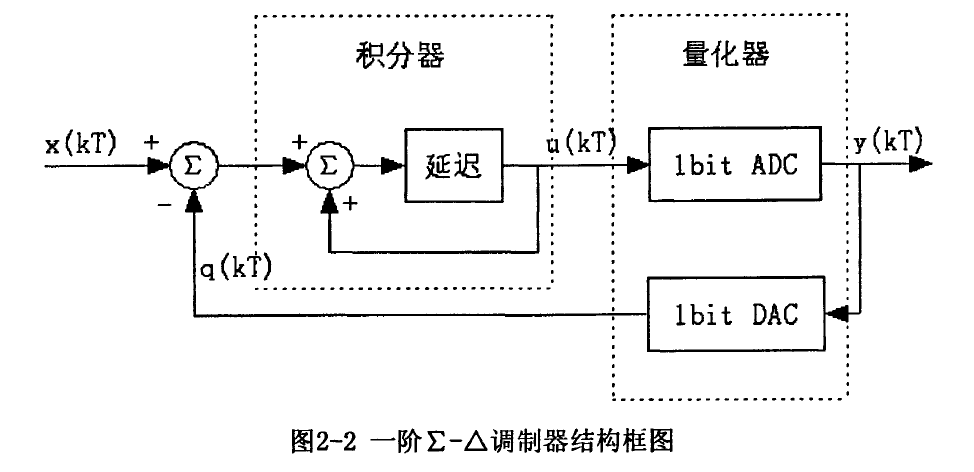

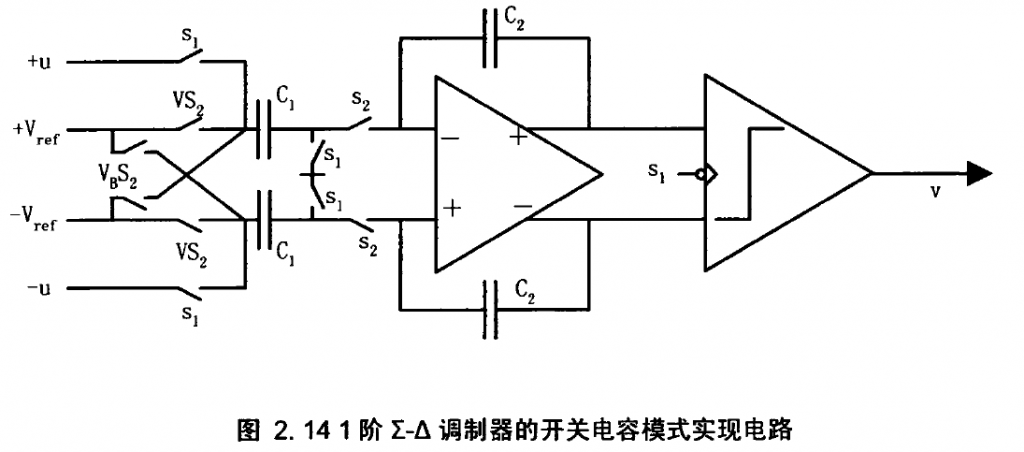

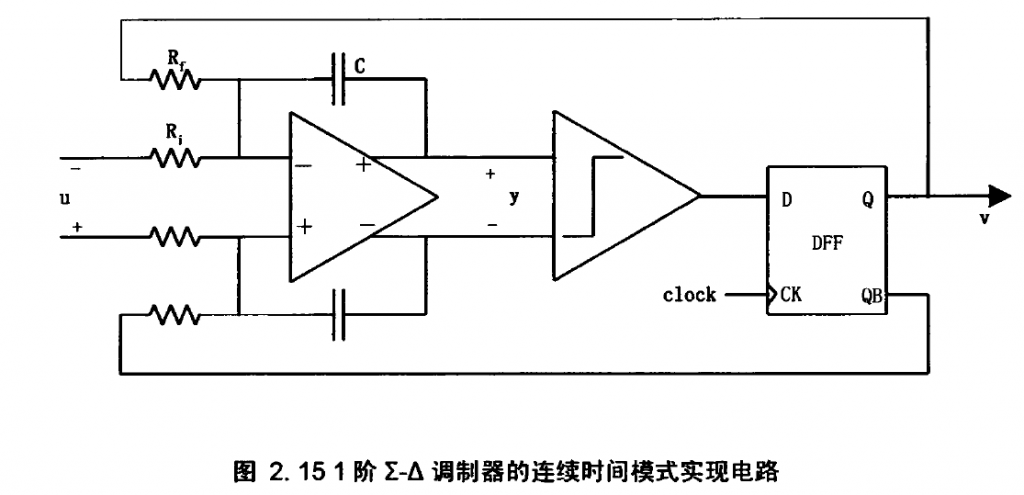

Σ-△ 调制器的实现方式可以分为两大类离散时间模式(开关电容电路实现)和连续时间模式。图2.14和图2.15巧分别为

一阶 Σ-△ 调制器的开关电容模式实现电路和连续时间模式实现电路。

18.开关电容的热噪声

接触IC设计已经一年半了,刚开始的激情和好奇已经所剩无几了,很多原理性的东西都需要一大堆让人头大的复杂公式推导和扎实的基础,而工程性的东西熟悉了流程之后也变得非常枯燥。所幸还有eetop,还有这么多同行前辈能在一起隔空探讨,除了论坛之外,收获最大的是guojun的博客,http://www.eetop.cn/blog/html/90/757190-type-blog.html 新开博客,我也写点简单的东西吧,希望能对其它人少走弯路,而不是成为互联网的垃圾。 关于开关电容噪声Boris Murmann已经分析并用不同的方法仿真验证过了,然而我网上和项目中接触到的不少人都是凭经验、仿真、测试甚至是别人家的论文或者项目估计得到的,所以还是郑重推荐一下他的论文,毕竟噪声决定着一个高精度AD的电容大小和功耗。 对于一个采样保持电路而言,噪声有3部分,一部分是通常提到的2kT/C,一部分是与运放和运放等效负载电容相关,最后一部分与开关电阻有关系,Boris Murman提到gmRon<<1时第三部分噪声可以忽略。所以总的噪声大约是2~6kT/C. 具体的值可以推导,再加以仿真验证,严格按照B.murmann的论文来推导和仿真吧。 新手容易犯的问题(大部分是我犯过的错误):1、噪声积分应该是从0~fs/2,而不是0~fs;2、pss+pnoise仿真时maxsideband和maxacfrequence一定要严格按照论文里面说的认真计算,而且这两个值越大仿真得到的噪声值越大也越准确;3、噪声推导一定要结合自己项目开关电容的结构,而不是直接套用其它类似结构的噪声公式,不同结构噪声可能会有区别; 推荐看了B.Murman的论文之后,从最简单的一个开关加一个电容的结构入手,仿一下噪声,结果是否为准确的kT/C来验证你的仿真方法没错。开关可以用analoglib中的理想开关switch,再加一个电阻并设置为产生噪声。 然后一步步推导和仿真验证。

19.SAR ADC的速度

20. sigma-delta ADC速度

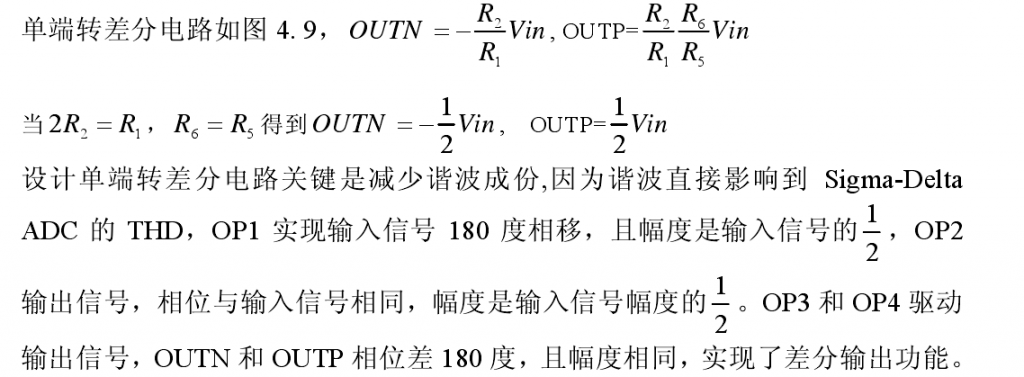

本文设计目标是通过 sigma-delta 调制器和数字抽取滤波器的优化设计,实现低功耗 16bit 音频采样系統设计,数字模拟电路总功耗小于 10m W,信号带宽是 20KHz(数字输出率 44.1 or 48KHz),信噪失真比 SNDR 大于 88d B,有效精度 15bits;当输入信号频率为 1k Hz,幅度是 1V 时,THD@0db FS 大于 90d B(有效精度 15bbit)。《16比特低功耗音频应用Si…ma-DeltaADC研究_刘志明》

数字抽取滤波器的主要目标是将输入信号带宽外的噪声(如量化噪声、调制器产生的噪声和前置滤波器没有滤掉的输入信号内的噪声)滤除掉。滤除后的基带应只剩下小部分量化噪声,因此提高了量化信噪比,即相当于增加了数字输出的有效分辨率。由于Σ一△调制器的输出为高速低分辨率的数据流,为了降低Σ一△调制器的数据输出率得到最终的转换结果,必须进行数字抽取。数字抽取实际上是实现将采样频率降至奈奎斯特频率并且将字长增加到相应位数,从而获得高分辨率的量化信号的过程。相对于最终的采样频率Fs,数字抽取滤波器还必须起到抗混叠滤波器的作用。在进行数字抽取的过程中,调制器输出的高速低分辨率数据流经过抽取后得到了低速高分辨率信号,因此抽取过程实际上是一个对信号进行重采样的过程,因而会引入混迭失真。为了防止混叠发生,必须对信号进行低通滤波。所以数字抽取滤波器还起到了抗混叠滤波的作用。

sigma-delta ADC matlab代码 :附录5.1 从入门到精通_[刘明亮 著]

真差分、4 × 2 多路复用器、模拟前端、同步采样 ADC 电路,讨论了ADC转化时间与获取时间的关系

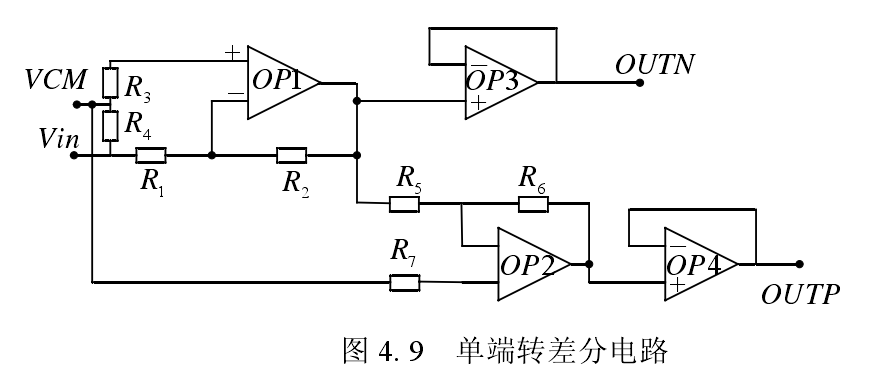

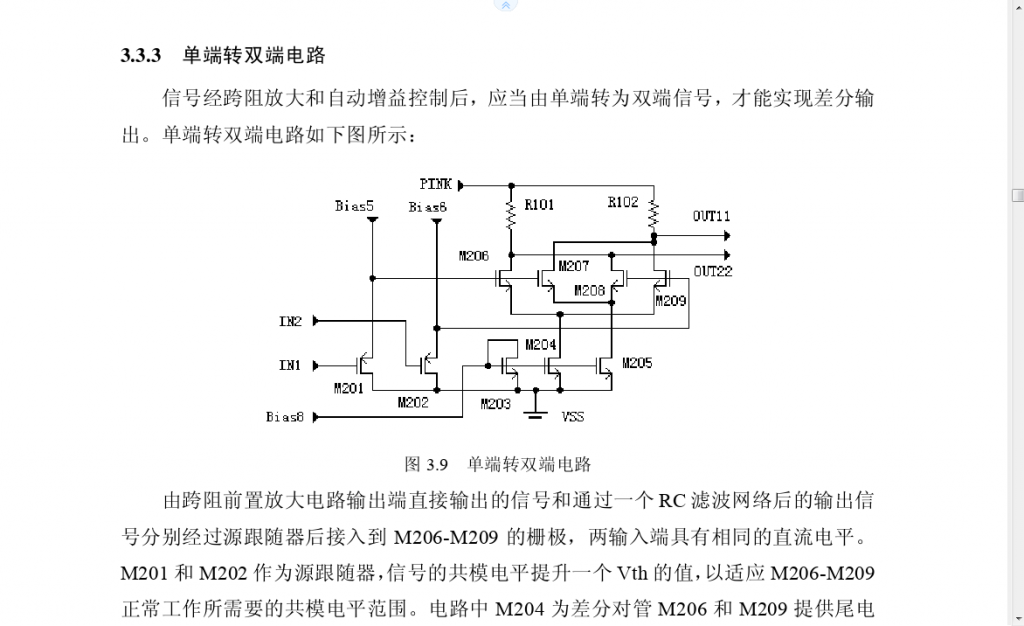

21.单端转差分电路

16比特低功耗音频应用Si…ma-DeltaADC研究_刘志明

全差分运放在虚拟机中的位置:/opt/Cadence/ASSURA4/tools.lnx86/dfII/samples/Verifier/VerifierExamples/full_diff_opamp_AC_run

22.CMOS制程噪声汇总

关于Cox,可以看这里:Cox是如何计算的

23.闩锁效应

闭环微加速度计接口全差分ASIC电路的设计_李海涛

由于标准工艺技术中的器件结构本身包含交替的层,当工艺的特征尺寸越来越小,在设计电路时必须要注意的一个效应是锁存现象。对于一个简单的经典反相器,如果两个栅极连接在一起充当反相器的输入,其横截面图如图示。

当两个晶体管被制造的时候形成两个寄生双极型晶体管:一个平行的和一个垂直的。沟道晶体管的源极形成寄生平行的晶体管的反射极,衬底为基极,阱形成集电极。沟道晶体管的源极形成寄生垂直的晶体管的发射极,阱形成基极,型衬底形成集电极。在正常情况下,结构中的结为反向偏置。然而,如果两个双极型晶体管的发射极因某种原因,工作在放大区,电路会出现正反馈,引起两个晶体管传导剧烈。这种效应产生的根本原因是在设计集成电路时产生的寄生三极管的发射结上产生了正向偏压,当寄生三极管闭环增益大于时这个条件很容易满足,就会出现过高的电流引起电路的某一部分损坏。

通常我们的做法就是保证、和β足够小来避免这一问题,垂直的双极型晶体管的β由工艺特性决定,正如阱深不受电路设计者的控制。但是,横向双极型晶体管的β可以通过增加基极宽度即沟道晶体管的源极到型阱的距离而减少。在器件周围采用接电源地的保护环,降低横向电阻和横向电流密度,增加并合理安排衬底及阱区分别对地、电源的接触孔,减小电位梯度。电源地的接触孔应尽可能多地安排在靠近阱的边缘处,并使电源地接触孔相互对应。图是一个设计用来抑制效应的保护环。

24.Veriloga代码for sigma-delta ADC 和 pipeline ADC

sigma-dleta ADC

module comparator(cout, inp, inm);

output cout;

input inp, inm;

electrical cout, inp, inm;

parameter real td = 1n, tr = 1n, tf = 1n;

real vcout;

analog begin

@(cross(V(inp) - V(inm), 0))

vcout = ((V(inp) > V(inm)) ? 1 : 0);

V(cout) <+ transition(vcout, td, tr, tf);

end

endmodule

module integrator(out, in);

output out;

input in;

electrical in, out;

parameter real gain = 1.0;

parameter real ic = 0.0;

analog begin

V(out) <+ gain*idt(V(in), ic);

end

endmodule

module sigmadelta(out, aref, in);

output out;

input aref, in;

ground gnd;

comparator C1(.cout(aa0), .inp(in), .inm(aa2));

integrator #(1.0) I1(.out(aa1), .in(aa0));

comparator C2(out, aa1, gnd);

d2a #(.width(1)) D1(aa2, aref, out); // a D/A converter

endmodulepipeline ADC

module pipeline_adc (in, out);

parameter bits=8, fullscale=1.0;

inout in;

inout [0:bits-1] out;

electrical in;

electrical [0:bits-1] out;

comparator #(.ref(fullscale/2)) cmp (in, out[bits-1]);

generate

if (bits > 1) begin

electrical n1, n2;

subtractor #(.level(fullscale)) sub (in, out[bits-1], n1);

amp2x amp (n1, n2);

pipeline_adc #(.bits(bits-1)) section (n2, out[0:bits-2]);

end

endgenerate

endmoduleVerilog-AMS Language Reference Manual(veriloga)

一阶连续时间 sigma-delta ADC 系统仿真(含代码和教程)在何乐年《模拟集成电路设计与仿真》p328,模块全部用verilog-a实现,有全部教程。

25.相关双采样

T6-II.1a: Correlated Double Sampling

Characterization of surface channel CCD image arrays at low light levels

Noise transfer characteristics of a correlated double sampling circuit

AD9823 相关双采样器(CDS)-》通用型电子倍增CCD驱动系统及其方法

带有CDS的缓冲输出级电路完整分析

26.CMOS 4T像素

3T and 4T pixel analysis for cmos image sensor 3T and 4T pixel analysis for cmos image sensor

27.PSS+PNOISE仿真

CMOS模拟集成电路设计与仿真实例——基于Cadence ADE,p142,p210

28.工频干扰

【1】流水线ADC的前台校准方法

29.从cadence中将数据导出,matlab画ADC信噪比和频谱图程序

参考何乐年《模拟集成电路设计与仿真》p338。

30.广义传输函数

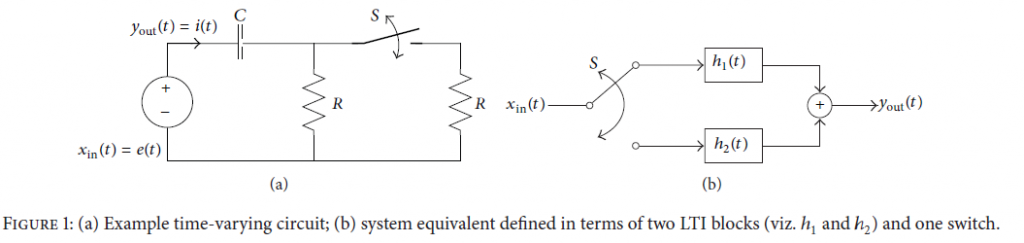

Steady-State Response of Periodically Switched Linear Circuits via Augmented Time-Invariant Nodal Analysis

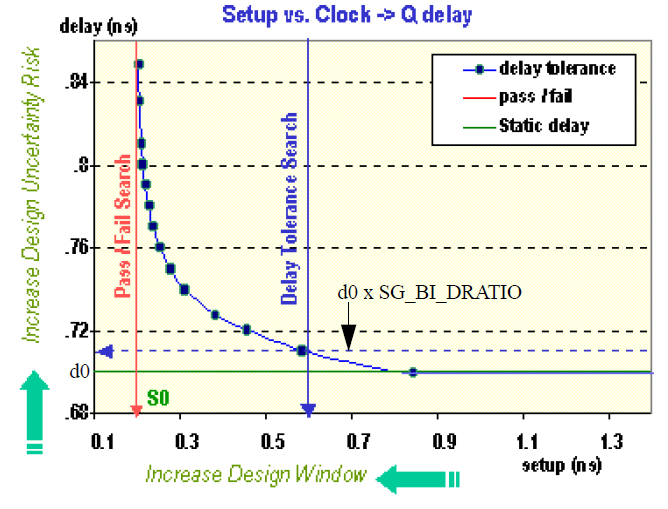

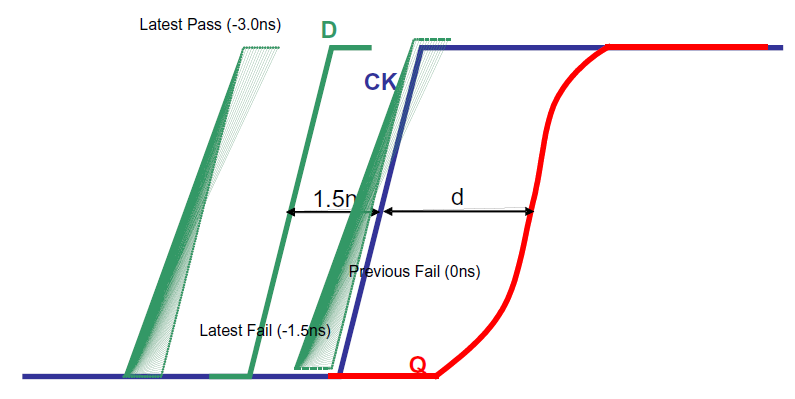

30《CMOS集成电路后端设计与实战》——3.3 标准单元设计流程,建立标准单元库,Signalstorm

《CMOS集成电路后端设计与实战》——3.3 标准单元设计流程

本文最后百度网盘分享有《SignalStorm® Library Characterizer User Guide》,这是一本很有价值的手册,其中描述了如何建立一个标准单元库,建立时间的二分查找,ECMS模型等等重要问题。在该手册的第33页,有如下的建立时间与传输延时的关系图演示。

31. 氧化钒的比探测率到底是多少?

通过《非制冷红外焦平面探测器芯片一体化设计及关键技术研究_阙隆成》中的公式,结合一些测试结果,计算得到约为1.25e7左右,计算代码如下。

h = 6.62e-34;

c= 3e8;

epsilon_t = 1;

k = 1.38e-23;

T = 300;

fun = @(x) 2.*h*c.^2*epsilon_t./(x.^5.*(exp(h*c./(x*k*T))-1));

L = integral(fun,8e-6,14e-6)

F = 1;

A = 25*25e-12;

P = L*A*pi/(4*F^2)

I = 8e-6*0.02;

R = I/P

NEP = 2e-11;%噪声按50mK重新代入计算得到。

B = 100; %Hz

D_star = sqrt(A*B)/NEP32 bandgap噪声到底有多少?

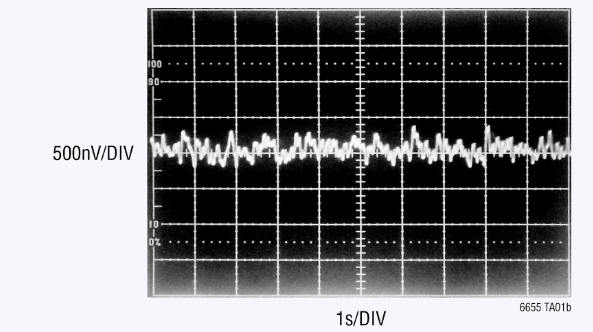

A Sub-1-V Low-Noise Bandgap Voltage Reference 0.5um工艺,1hz处100nV/sqrt(Hz),接近0Hz处500 nV/sqrt(Hz)

为何基准电压噪声非常重要? 芯片LTC6655, 1hz处100nV/sqrt(Hz) ,0.1hz处1100 nV/sqrt(Hz)

仔细分析阵列器件的工作过程,现在(2024年5月)感觉是电源的噪声占主导,因为对于大规模阵列来说,像元之间的信号不同也是噪声的来源,这样就不能只考虑低频的噪声了。对于 LTC6655,90nV/sqrt(Hz) ,对于1024*512半边阵列60Hz来说,带宽为15.7MHz,噪声为357uV。而假若考虑到512同时采样,这样带宽就成了15.7MHz/512=30kHz,相应的噪声也变成了约70uV。

参考文献

【2】非制冷红外焦平面探测器芯片一体化设计及关键技术研究