本文摘抄于:《高性能小数分频模拟锁相环关键技术研究》

1.1 研究背景

随着信息技术的发展,人们的沟通交流变得越来越方便,同时集成电路技术的进步使得射频收发机集成度越来越高。射频收发机是无线通信设备中重要的元件,它可以接收和发射无线信号,频率综合器是收发机中的关键模块,它为信号的上变频和下变频提供本振信号,是基带信号和射频信号间的桥梁[1]。

频率综合器输出信号的纯度决定着收发机的性能,其功耗占整个收发机的大部分。根据频率合成方法主要有三种类型的频率综合器,分别是直接数字频率综合器,直接模拟频率综合器和基于锁相环电路的频率综合器。其中基于锁相环的频率综合器具有低成本、低功耗和输出频谱纯度高等优点而被广泛使用[2]。

按照分频比类型频率综合器主要分为两种,一种的输出频率是参考频率的整数倍,参考频率通常是固定的,这种频率综合器称为整数N频率综合器;通常应用在FM收音机、TV接收机等类似设备中。这种结构的优点是设计相对简单,不需要后面提到的分数型锁相环需要的ΔΣ调制器,所以也不会有差分积分量化噪声。整数锁相环的另一个优点是,参考时钟频率和振荡器频率为整数关系,这样就可以利用二者之间的

谐波注入锁定来实现锁相环。从电路设计上来讲,由于分频器只工作在一个固定的分频比,其设计要求也较简单[3]。在输出频率变化要求不高的应用中,如在时钟恢复应用中,整数型锁相环架构是最优的选择,但是对于要求实现很多不同的输出频率的应用中,如射频频率综合器,整数型锁相环就表现出很大的局限性。比如,GSM通信系统需要生成最小间距为200k Hz的频率,由于整数型锁相环只能采用整数分频比,所以其输入参考频率最高只能为200k Hz。一般锁相环的带宽通常要小于参考频率的1/10[4],那么锁相环最高带宽只能在10~20k Hz。也就是说,整数锁相环环路带宽的取值,会受到生成分辨率要求的限制。如果生成频率的分辨率很高,那么锁相环带宽只能非常窄。锁相环环路带宽过小会产生许多问题,由于振荡器的噪声主要是在高频段的,环路带宽过小就会增大振荡器高频噪声的影响。其次过窄的锁相环带宽会使振荡器难以克服发射器的牵引。而且低参考时钟频率意味着高分频比和大量的噪声混叠,所以整数型锁相环,其带内相位噪声指标一般比较差,难以满足无线通信标准的要求。小数锁相环相的特点是可以产生分数的分频比。小数型锁相环的分频比在不同参考时

钟周期可以采用不同的整数值,这样其“平均”分频比就可以是一个非整数的值。因此结合实验室项目需要,本课题决定研究ΔΣ小数型频率综合器。

1.2 锁相环研究现状

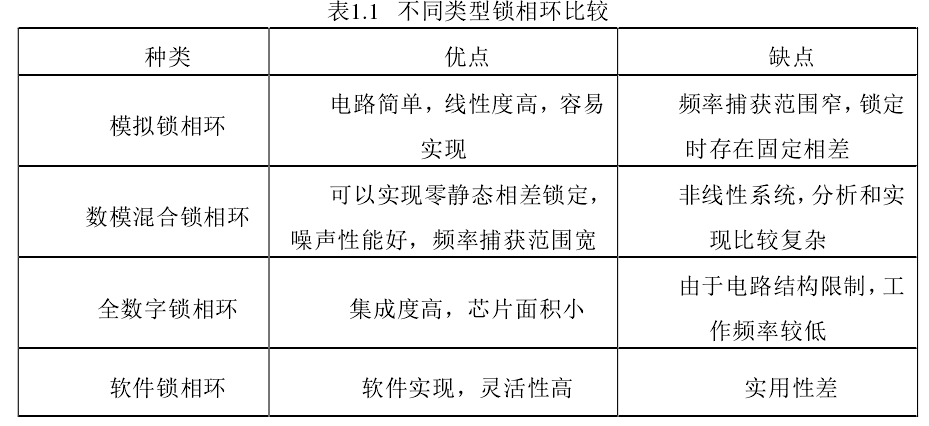

早在上世纪30年代锁相环的概念就被提出来了,早在1932年,法国工程师贝尔赛什就设计出了第一个PLL。最早的锁相环是由分立元件来实现的,随着集成电路技术的飞速发展,集成锁相环得到了更加广泛的应用。第一个片上集成PLL大约出现在1964年,是一个完全的模拟器件。由模拟鉴相器、环路滤波器和压控振荡器三部分组成。模拟鉴相器由模拟乘法器实现,这种结构实现的锁相环叫做线性锁相环(LPLL)[5,6]。之后的几年,随着晶体管尺寸的不断缩小,锁相环中的鉴相器部分使用数字电路来实现,加上数字电路实现的分频器组成频率综合器,这种类型的锁相环被称为数模混合锁相环,随后,锁相环转移到数字电路电路领域,大约在上世纪70年代,出现了第一个全数字锁相环(ADPLL)[7]。这类锁相环中不使用电容电阻等无源器件,芯片面积小。类似滤波器,PLL也可以使用软件来实现,这种锁相环的功能由软件程序来实现,不需要特定的硬件支撑,这种锁相环被称为SPLL。

目前看来,模拟锁相环由于频率捕获范围窄,实用性差,已基本被淘汰;全数字锁相环由于结构灵活、集成度高和频率转换速度快等优点,已成为近几年的研究热点,但是其频率上限限制了其应用范围;数模混合锁相环输出频谱纯度高,应用范围广,成本较低,得到了广泛的关注和研究。是目前广泛使用的锁相环架构。根据分频比类型不同又可分为整数型锁相环(integer N PLL)和分数型锁相环(fractional- N PLL),又叫小数分频锁相环。整数型锁相环的分频比只能是整数值,而分数型锁相环的分频比既可以是整数也可以是分数。分数型锁相环的分频比更灵活,不会像整数型锁相环那样受过低参考时钟频率限制,可以在低频参考时钟的前提下,实现更宽的带宽和快速锁定[8]。缺点是电路也更加复杂,引入额外的差分积分调试器(delta-sigma modulator ,DSM),需要处理分数杂散问题。

锁相环的应用主要有通信系统中的频率合成器、用于微处理的时钟生成以及时钟恢复电路中。不同应用的侧重要求也不同。频率综合器主要关注的是相位噪声、杂散、锁定时间这些指标,目前的趋势是在低电压条件下实现低功耗、高频谱纯度、以及快速锁定。这些公司有许多成熟的产品,如ADI公司的ADF5356小数分频频率综合器,时钟参考频率为600MHz,整数频带噪声基底为-227d Bc/Hz,小数噪声基底为-225d Bc/Hz。又如TI公司的LMX2571小数分频器产品,输出频率范围为10MHz到1344MHz,1MHz偏移@480MHz时为-145dBc/Hz

。比如LMX2594是一款高性能宽带合成器,输出频率可以从10MHz至15GHz。在100k Hz偏移和15GHz载波的情况下具有-110d Bc/Hz

的相位噪声。学术界上关于PLL的研究一直是热点方向。

2017年Yuming He,Yao-Hong Liu等人发表的一款输出频率为1.8GHz到2.5GHz的数字小数分频锁相环,整个芯片超低功耗只有673μW[9]。2017年Chih-Wei Yao,Wing Fai Loke等人在14nm CMOS工艺下设计的小数分频锁相环只有0.14ps的rms抖动和-78d Bc

的分数杂散[10]。还有日本的Huy Cu Ngo,Kengo Nakata等人设计的频率综合器,有0.42ps的抖动和-241.7d B的FOM[11]。

国内关于锁相环的研究起步较晚,目前仍与国外先进方向有一些距离,但是进步速度很快。国内公司如海思、芯原微电子等技术表现较为强劲。其中海思公司已经研究出振荡频率在70GHz以上的锁相环频率综合器。可以提供模块化高性能电路设计。国内高校对锁相环的研究也如火如荼。包括复旦大学、清华大学、浙江大学、东南大学和西安电子科技大学等。东南大学的吴建辉基于SMIC 0.18μm CMOS工艺,设计的小数分频锁相环能够达到快速锁定,输出相位噪声低于-110d Bc/Hz@1MHz[12]。西安电子科技大学的梁亮博士,基于0.13μm CMOS

工艺,设计了低电压小数分频频率综合器,功耗为12.5m W[13]。

目前锁相环频率综合器的研究方向是高频率、宽频带低相位噪声输出。保证频率分辨率的前提下快速锁定;低电压条件下的设计,降低整个系统的功耗。高性能的锁相环频率综合器在学术研究和生产中具有实际意义。

4.1.2 电路结构的选取

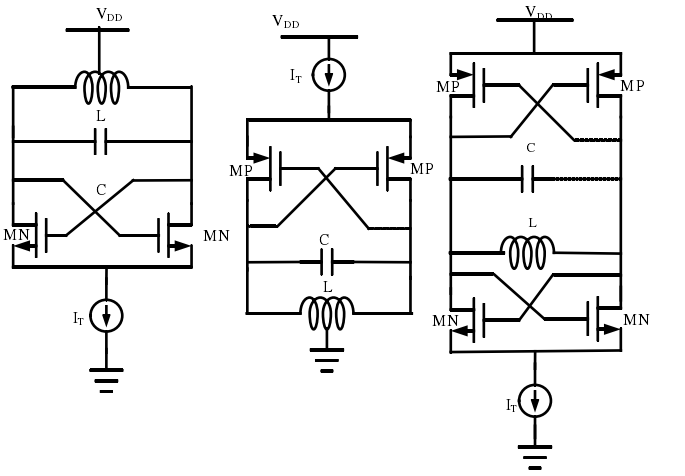

选择交叉耦合(负跨导)结构的LC振荡器来完成设计。这种结构的振荡器结构简单且容易起振。LC谐振腔起到振荡的作用,交叉耦合管起到负阻的作用,抵消电路振荡时损耗的能量。

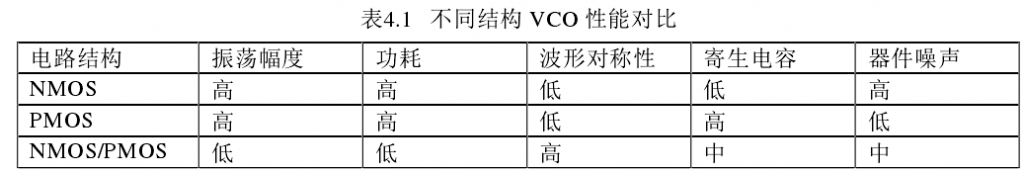

根据交叉偶合管形式的不同,可以将LCVCO分为以下三种类型(a)NMOS型耦合对,(b)PMOS型耦合对,(c)NMOS/PMOS型互补交叉耦合对。这三种结构的负阻值大小分别为:−2/?mn、−2/???以及−2/(???+???),???和???分别表示N型和P型MOS管的小信号跨导。其中,NMOS管的载流子迁移率约是PMOS管迁移率的3倍,在使用相同偏置电流的情况下,NMOS管耦合对的尺寸大约是

PMOS管尺寸的1/3左右,所以,NMOS型的VCO的调谐范围最宽和振荡频率最高。但是它的器件噪声是这三者中最大的。PMOS耦合管是三者当中器件噪声最小的。而互补型MOS管的VCO的输出振幅最大,它的输出具有比较好的波形对称性。由于其产生的负阻为单个NMOS

或PMOS的二倍,所以用一半的功耗就可以产生与单端相同的振幅。有利于降低功耗[36]。但是互补MOS结构会受到电压裕度的限制,不太适合在低电压条件下工作。

三种结构的对比如下表:

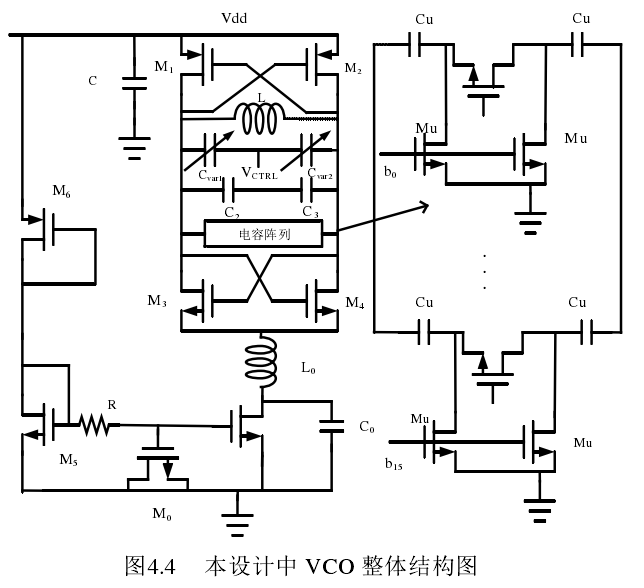

本设计中NMOS/PMOS交叉耦合对结构用来5GHz PLL的设计,其波形对称性好,功耗比较低,噪声也是比较适中的,有利于降低

VCO的相位噪声。

图4.4是本文设计的宽频带VCO的结构图,图中除谐振腔和NMOS/PMOS负阻外,可变电容管Cvar1,2用于实现频率的细调,即在选择一个频带之后实现频率的连续变化。电容阵列采用的二进制的开关电容阵列,共有4位16个相同的电容阵列,可以有16个不同频率范围的子带,电容选用MIM电容,原因是这种电容的品质因数Q值较高,有利于减小相位噪声。电感L0和电容C0组成的二倍频滤波网络,可以减小

二倍频附近的噪声分量,阻止其进入振荡回路中。电容C的作用是滤除掉电源噪声的影响。连接成二极管形式的M5和M6两个晶体管形成的自偏置电路镜,通过调整M5和M6的大小来改变电源提供的电流大小。电阻R和M0形成的低通滤波网络,减小电流的干扰噪声。

果偏置电流大小为?bias,则VCO单边输出电压峰峰值为:

参考文章

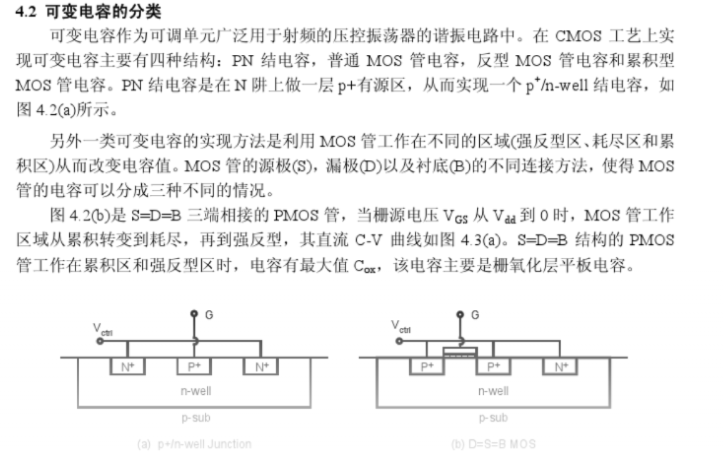

可变电容电路以及包含该可变电容电路的集成电路

复旦大学,专用集成电路与系统国家重点实验室,唐长文:MOS管可变电容的C-V曲线

复旦大学唐长文博士论文:电感电容压控振荡器