摘要:

锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。本文将参考上述各种应用来介绍PLL电路的一些构建模块,以指导器件选择和每种不同应用内部的权衡考虑,这对新手和PLL专家均有帮助。本文参考ADI公司的ADF4xxx和HMCxxx系列PLL和压控振荡器(VCO),并使用ADIsimPLL(ADI公司内部PLL电路仿真器)来演示不同电路性能参数。

基本配置:时钟净化电路

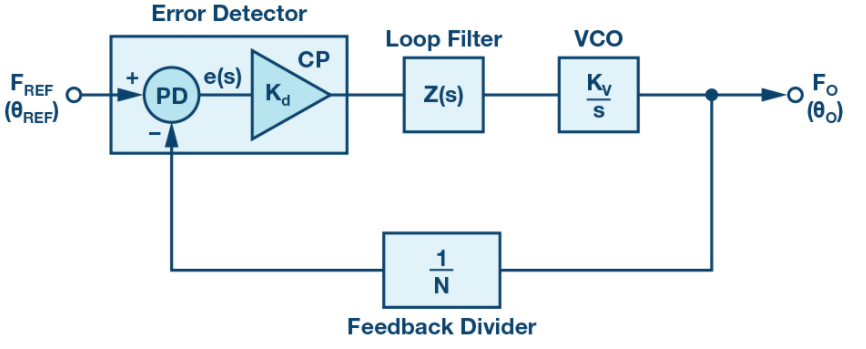

锁相环的最基本配置是将参考信号(FREF)的相位与可调反馈信号(RFIN)F0的相位进行比较,如图1所示。图2中有一个在频域中工作的负反馈控制环路。当比较结果处于稳态,即输出频率和相位与误差检测器的输入频率和相位匹配时,我们说PLL被锁定。就本文而言,我们仅考虑ADI公司ADF4xxx系列PLL所实现的经典数字PLL架构。

该电路的第一个基本元件是鉴频鉴相器(PFD)。PFD将输入到REFIN的频率和相位与反馈到RFIN的频率和相位进行比较。ADF4002 是一 款可配置为独立PFD(反馈分频器N = 1)的PLL。因此,它可以与高质量压控晶体振荡器(VCXO)和窄低通滤波器一起使用,以净化高噪声REFIN时钟。

鉴频鉴相器

图3中的鉴频鉴相器将+IN端的FREF输入与和-IN端的反馈信号进行比较。它使用两个D型触发器和一个延迟元件。一路Q输出使能正电流源,另一路Q输出使能负电流源。这些电流源就是所谓电荷泵。有关PFD操作的更多详细信息,请参阅”用于高频接收器 和发射器的锁相环“。

使用这种架构,下面+IN端的输入频率高于-IN端(图4),电荷泵输出会推高电流,其在PLL低通滤波器中积分后,会使VCO调谐电压上升。这样,-IN频率将随着VCO频率的提高而提高,两个PFD输入最终会收敛或锁定到相同频率(图5)。如果-IN频率高于+IN频率,则发生相反的情况。

回到原先需要净化的高噪声时钟例子,时钟、自由运行VCXO和闭环PLL的相位噪声曲线可以在ADIsimPLL中建模。

从所示的ADIsimPLL曲线中可以看出,REFIN的高相位噪声(图6)由低通滤波器滤除。由PLL的参考和PFD电路贡献的所有带内噪声都被低通滤波器滤除,只在环路带宽外(图8)留下低得多的VCXO噪声(图7)。当输出频率等于输入频率时,PLL配置最简单。这种PLL称为时钟净化PLL。对于此类时钟净化应用,建议使用窄带宽(<1kHz)低通滤波器。

高频整数N分频架构

为了产生一系列更高频率,应使用VCO,其调谐范围比VCXO更宽。这常用于跳频或扩频跳频(FHSS)应用中。在这种PLL中,输出是参考频率的很多倍。压控振荡器含有可变调谐元件,例如变容二极管,其电容随输入电压而改变,形成一个可调谐振电路,从而可以产生一系列频率(图9)。PLL可以被认为是该VCO的控制系统。

反馈分频器用于将VCO频率分频为PFD频率,从而允许PLL生成PFD频率倍数的输出频率。分频器也可以用在参考路径中,这样就可以使用比PFD频率更高的参考频率。ADI公司的 ADF4108 就是这样的PLL。PLL计数器是电路中要考虑的第二个基本元件。

PLL的关键性能参数是相位噪声、频率合成过程中的多余副产物或杂散频率(简称杂散)。对于整数N PLL分频,杂散频率由PFD频率产生。来自电荷泵的漏电流会调制VCO的调谐端口。低通滤波器可减轻这种影响,而且带宽越窄,对杂散频率的滤波越强。理想单音信号没有噪声或额外杂散频率(图10),但在实际应用中,相位噪声像裙摆一样出现在载波边缘,如图11所示。单边带相位噪声是指在距离载波的指定频率偏移处,1 Hz带宽内相对于载波的噪声功率。

整数N和小数N分频器

在窄带应用中,通道间隔很窄(通常<5MHz),反馈计数器N很高。通过使用双模P/P + 1预分频器,如图12所示,可以利用一个小电路获得高N值,并且N值可以利用公式N = PB + A来计算;以8/9预分频器和90的N值为例,计算可得B值为11,A值为2。对于A或2个周期,双模预分频器将进行9分频。对于剩余的(B-A)或9个周期,它将进行8分频,如表1所示。预分频器一般利用较高频率电路技术设计,例如双极性射极耦合逻辑(ECL)电路,而A和B计数器可以接受这种较低频率的预分频器输出,它们可以利用低速CMOS电路制造,以减少电路面积和功耗。像ADF4002这样的低频净化PLL省去了预分频器。

| N Value | P/P + 1 | B Value | A Value |

| 90 | 9 | 11 | 2 |

| 81 | 9 | 10 | 1 |

| 72 | 8 | 9 | 0 |

| 64 | 8 | 8 | 0 |

| 56 | 8 | 7 | 0 |

| 48 | 8 | 6 | 0 |

| 40 | 8 | 5 | 0 |

| 32 | 8 | 4 | 0 |

| 24 | 8 | 3 | 0 |

| 16 | 8 | 2 | 0 |

| 8 | 8 | 1 | 0 |

| 0 | 8 | 0 | 0 |

带内(PLL环路滤波器带宽内)相位噪声受N值直接影响,带内噪声增幅为20log(N)。因此,对于N值很高的窄带应用,带内噪声主要由高N值决定。利用小数N分频合成器(例如 ADF4159 或 HMC704),可以实现N值低得多但仍有精细分辨率的系统。这样一来,带内相位噪声可以大大降低。图13至图16说明了其实现原理。在这些示例中,使用两个PLL来生成适合于5G系统本振(LO)的7.4 GHz至7.6 GHz频率,通道分辨率为1 MHz。ADF4108以整数N分频配置使用(图13),HMC704以小数N分频配置使用。HMC704(图14)可以使用50 MHz PFD频率,这会降低N值,从而降低带内噪声,同时仍然支持1 MHz(或更小)的频率步长——可注意到性能改善15 dB(在8 kHz偏移频率处)(图15与图16对比)。但是,ADF4108必须使用1 MHz PFD才能实现相同的分辨率。

对于小数N分频PLL务必要小心,确保杂散不会降低系统性能。对于HMC704之类的PLL,整数边界杂散(当N值的小数部分接近0或1时产生,例如147.98或148.02非常接近整数值148)最需要关注。解决措施是对VCO输出到RF输入进行缓冲,以及/或者做精心的规划频率,改变REFIN以避免易发生问题的频率。

对于大多数PLL,带内噪声高度依赖于N值,也取决于PFD频率。从带内相位噪声测量结果的平坦部分减去20log(N)和10log(FPFD)得到品质因数(FOM)。选择PLL的常用指标是比较FOM。影响带内噪声的另一个因素是1/f噪声,它取决于器件的输出频率。FOM贡献和1/f噪声,再加上参考噪声,决定了PLL系统的带内噪声。

用于5G通信的窄带LO

对于通信系统,从PLL角度来看,主要规格有误差矢量幅度(EVM)和VCO阻塞。EVM在范围上与积分相位噪声类似,考虑的是一系列偏移上的噪声贡献。对于前面列出的5G系统,积分限非常宽,从1 kHz开始持续到100 MHz。EVM可被认为是理想调制信号相对于理想点的性能降幅百分比(图17)。类似地,积分相位噪声将相对于载波的不同偏移处的噪声功率进行积分,表示通过配置可以计算EVM、积分相位噪声、均方根相位误差和抖动。现代信号源分析仪也会包含这些数值(图18),只需按一下按钮即可得到。随着调制方案中密度的增加,EVM变得非常重要。对于16-QAM,根据ETSI规范3GPP TS 36.104,EVM最低要求为12.5%。对于64-QAM,该要求为8%。然而,由于EVM包括各种其他非理想参数(功率放大器失真和不需要的混频产物引起),因此积分噪声通常有单独的定义(以dBc为单位)。

VCO阻塞规范在需要考虑强发射存在的蜂窝系统中非常重要。如果接收器信号很弱,并且VCO噪声太高,那么附近的发射器信号可能会向下混频,淹没目标信号(图19)。图19演示了如果接收器VCO噪声很高,附近的发射器(相距800 kHz)以-25 dBm功率发射时,如何淹没-101 dBm的目标信号。这些规范构成无线通信标准的一部分。阻塞规范直接影响VCO的性能要求。

压控振荡器(VCO)

我们的电路中需要考虑的下一个PLL电路元件是压控振荡器。对于VCO,相位噪声、频率覆盖范围和功耗之间的权衡十分重要。振荡器的品质因数(Q)越高,VCO相位噪声越低。然而,较高Q电路的频率范围比较窄。提高电源电压也会降低相位噪声。在ADI公司的VCO系列中, HMC507 的覆盖范围为6650 MHz至7650 MHz,100 kHz时的VCO噪声约为-115 dBc/Hz。相比之下, HMC586 覆盖了从4000 MHz 到8000 MHz的全部倍频程,但相位噪声较高,为-100 dBc/Hz。为使这种VCO的相位噪声最小,一种策略是提高VCO调谐电压VTUNE的范围(可达20 V或更高)。这会增加PLL电路的复杂性,因为大多数PLL电荷泵只能调谐到5 V,所以利用一个由运算放大器组成的有源滤波器来提高PLL电路的调谐电压。

多频段集成PLL和VCO

另一种扩大频率覆盖范围而不恶化VCO相位噪声性能的策略是使用多频段VCO,其中重叠的频率范围用于覆盖一个倍频程的频率范围,较低频率可以利用VCO输出端的分频器产生。ADF4356就是这种器件,它使用四个主VCO内核,每个内核有256个重叠频率范围。该器件使用内部参考和反馈分频器来选择合适的VCO频段,此过程被称为VCO频段选择或自动校准。

多频段VCO的宽调谐范围使其适用于宽带仪器,可产生范围广泛的频率。此外,39位小数N分辨率使其成为精密频率应用的理想选择。在矢量网络分析仪等仪器中,超快开关速度至关重要。这可以通过使用非常宽的低通滤波器带宽来实现,它能非常快地调谐到最终频率。在这些应用中,通过使用查找表(针对每个频率直接写入频率值)可以绕过自动频率校准程序,也可以使用真正的单核宽带VCO,如HMC733 ,其复杂性更低。

对于锁相环电路,低通滤波器的带宽对系统建立时间有直接影响。低通滤波器是我们电路中的最后一个元件。如果建立时间至关重要,应将环路带宽增加到允许的最大带宽,以实现稳定锁定并满足相位噪声和杂散频率目标。通信链路中的窄带要求意味着使用HMC507时,为使积分噪声最小(30 kHz至100 MHz之间),低通滤波器的最佳带宽约为207 kHz(图20)。这会贡献大约-51 dBc的积分噪声,可在大约51μs内实现频率锁定,误差范围为1 kHz(图22)。

相比之下,宽带HMC586(覆盖4 GHz至8 GHz)以更接近300 kHz带宽的更宽带宽实现最佳均方根相位噪声(图21),积分噪声为-44 dBc。但是,它在不到27μs的时间内实现相同精度的频率锁定(图23)。正确的器件选择和周围电路设计对于实现应用的最佳结果至关重要。

低抖动时钟

对于高速数模转换器(DAC)和高速模数转换器(ADC),干净的低抖动采样时钟是必不可少的构建模块。为使带内噪声最小,应选择较低的N值;但为使杂散噪声最小,最好选择整数N值。时钟往往是固定频率,因此可以选择频率以确保REFIN频率恰好是输入频率的整数倍。这样可以保证PLL带内噪声最低。选择VCO(无论集成与否)时,须确保其噪声对应用而言足够低,尤其要注意宽带噪声。然后需要精心放置低通滤波器,以确保带内PLL噪声与VCO噪声相交——这样可确保均方根抖动最低。相位裕度为60°的低通滤波器可确保滤波器峰值最低,从而较大限度地减少抖动。这样的话,低抖动时钟就落在本文讨论的第一个电路的时钟净化应用和所讨论的最后一个电路的快速开关能力之间。

对于时钟电路,时钟的均方根抖动是关键性能参数。这可以利用ADIsimPLL估算,或使用信号源分析仪测量。对于像 ADF5356这样的 高性能PLL器件,相对较宽的低通滤波器带宽(132 kHz),配合WenxelOCXO之类的超低REFIN源,允许用户设计均方根抖动低于90 fs的时钟(图26)。操纵PLL环路滤波器带宽(LBW)的位置表明,如果降低太多,VCO噪声在偏移较小时(图24)将开始占主导地位,带内PLL噪声实际上会降低,而如果提高太多的话,带内噪声在偏移处占主导地位,VCO噪声则显著降低(图25)。

参考电路

Collins, Ian. “用于无线应用的集成PLL和VCO.” Radio Electronics, 2010年。

Curtin, Mike and Paul O’Brien. “用于高频接收器和发射器的锁相环。” 《模拟对话》,第33卷,1999年。

作者

Ian Collins

Ian Collins毕业于爱尔兰科克大学,拥有电气和电子工程学位并从2000年起在ADI公司的射频和微波部工作。他目前是微波频率生成部的应用经理,主要负责锁相环(PLL)和压控振荡器(VCO)产品方面的工作。非工作时间或不陪伴家人时,Ian喜欢摄影和戏剧(无论是在台上还是在台下)、阅读以及听音乐。