为什么模拟版图设计很难实现自动化呢?主要问题在于模拟设计的多因素性质。即使是一个简单的运算放大器,也可能需要对其输入偏置电流、失调电压、CMRR、PSRR、增益裕度、相位裕度、噪声、失真、电压摆幅等参数进行优化。模拟模块的版图设计会对以上所有因素造成影响。

1985年,英特尔推出了80386微处理器,它装载了275,000个晶体管,在当时令人惊叹。而到了2020年,苹果公司发行了首款自产微处理器M1,其中装载了160亿个晶体管。在短短35年的时间里,苹果公司最新器件所装载的晶体管数量比其前辈多了58,000倍。M1甚至不是市场上最大的处理器,据说Nvidia的GA100Ampere装载了约540亿个晶体管。

尽管80386的版图那时候很可能主要是使用当时的CAD工具人工设计的,但是苹果M1中的晶体管哪怕只有一个零头的版图设计有人为参与,也都是件不可思议的事情。在80年代中期,也就是80386微处理器发布的同时,Tangent Systems公司的EDA先驱们就几乎实现了数字版图设计的全自动化。当今大多数的数字工程师几乎很少考虑过电路的版图设计,当然更不会考虑单个晶体管的版图设计了。

如今,具有数以亿计器件的数字模块,通常通过先进的EDA工具在数小时内就能完成布局和布线,而几乎没有人力投入。这对数字设计生产效率的影响确实是巨大的。虽然M1背后的团队比最初的80386团队要大得多,但其总体版图设计的生产效率却比1985年高出至少三个数量级,即1000倍。

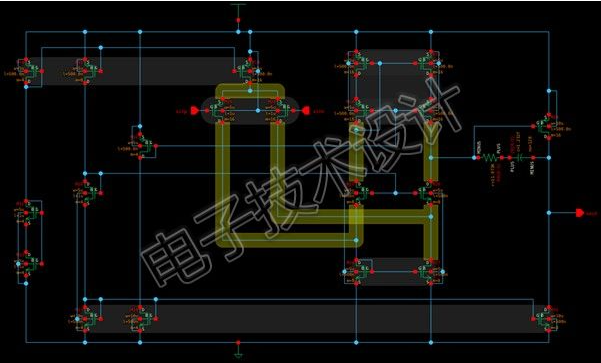

相反,自集成电路诞生以来,模拟版图设计就一直是项手动任务——而今对于大多数设计师而言,模拟IC版图设计也仍然是项手动工作。许多模拟版图设计师仍在手动布局各个晶体管,手动布线每条导线,并手动绘制每个阱的形状和保护环。在过去的几年,随着模板化版图设计的到来,尽管情况已有所改善,但模拟设计仍然是项非常耗时的任务。

多年来,许多在模拟设计流程方面渐进式的改变,也提高了该领域的版图设计生产效率,但这还远远不够。这些改变包括参数化单元、原理图驱动版图,以及近期的模板化版图。这些改变的总体影响可能多达10倍的提高。在1985年一个设计师可能要花三个星期才能完成的版图设计,现在可以在2-3天内完成。

生产效率提高10倍已经很不错了,不是吗?那问题出在哪里?问题在于,与此同时,工艺改变使得模拟设计的完成变得更加困难。如今,版图依赖效应已经变得至关重要,以至于无法预先确定最佳版图。工程师和设计师们经常需要对他们的设计进行4到5次的调整和重新设计,才能达到规格要求。实际上,生产效率的有效提高最多为2~3倍。

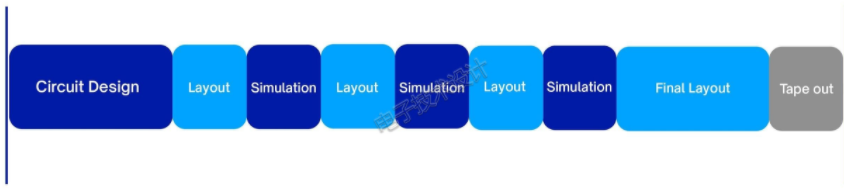

模拟版图设计已成为“循环版图设计”。电路工程师们需要尽快进行多次版图迭代,实现提取和仿真,以便能够完成设计。由于每次迭代都需要花费数小时或数天的时间,因此这是一个昂贵且耗时的方案。

就像Tangent和Tancell在1980年代实现了数字设计一样,模拟设计界迫切需要一种能够解决模拟版图设计自动化的变革性技术。模拟设计也应该向数字设计一样,从计算能力的增长中显著获益。我们需要逐步改进现有的手动版图设计技术,并真正实现模拟自动化。否则,模拟设计师们将继续成为IC设计界的灰姑娘,永远重复最不讨好的手动版图设计任务。

多因素性质

那么,为什么模拟版图设计很难实现自动化呢?主要问题在于模拟设计的多因素性质。即使是一个简单的运算放大器,也可能需要对其输入偏置电流、失调电压、CMRR、PSRR、增益裕度、相位裕度、噪声、失真、电压摆幅等参数进行优化。模拟模块的版图设计会对以上所有这些因素造成影响。

在数字案例中,标准单元方法可有效地将版图设计问题抽象为一个核心问题,即只需考虑三个需要优化的主要因素:时序、功耗和面积。创建标准单元库是一项复杂的自定义任务,但是一旦有了一个具有多种输出驱动强度的双输入与非门,就无需一遍又一遍地创建新的晶体管级版图。

这种抽象也意味着,数字自动化工具不必考虑绝大多数复杂的DRC规则。它们必须考虑布线层规则,但不用理会数以百计的决定有源层版图设计的复杂规则。自动进行数字版图设计的任务,主要是应用图论和计算机科学中的一种实践。这种表述虽然有些过于简化,但与自动化模拟版图设计相比也不为过。

数字MOSFET被强行驱动到饱和区工作,起到开关的作用,或开或关。在模拟设计中,MOSFET在其线性(欧姆)区工作,因此对其周围的版图环境就非常敏感。将模拟器件视为可像数字单元一样布局和布线的抽象模块,是根本不可能的。布线还会以复杂的方式影响模拟设计。在数字环境中,较长的布线对于信号延迟具有简单、可预测的影响。在模拟电路中,较长的布线会使电路的电容增加,这会对噪声、失真、频率响应等许多因素造成负面影响。

多年来,人们在将模拟版图设计自动化方面进行了诸多尝试。其中大多数都着眼于修改数字标准单元的方法,但都没有成功。这些算法对其所生成的解决方案会对电路性能产生什么样的影响并不了解。一些尝试采用了来自数字领域的布图规划技术。布图规划算法旨在将不规则形状有效封装到最小空间中。但是,模拟版图设计主要不是封装问题。实际上,尽管紧凑而节省空间的封装很重要,但它在模拟版图设计优先级列表中排名很靠后。

另一个问题是布线。在数字世界中,布局和布线是先后两步操作。首先是利用布局算法对标准单元进行布局。布局器能“顾及布线”,并能考虑布线拥堵以及来自导线的寄生电阻和寄生电容的影响,但它实际上并未对导线和标准单元进行同时布局。这种布线和布局相分离的方法不适用于模拟版图设计。可以用多晶硅接头的简单示例来说明这种情况。MOSFET栅极的连接点需要在多晶硅层留出空间而用于栅极的短距离扩展,以及连接到较高金属层的过孔。这种几何结构造成器件间在垂直方向上的距离越来越远,从而直接影响器件的布局。另外,这些多晶硅接头会增加多晶硅几何结构的数量,并影响多晶硅密度。超过某个阈值时,可能有必要横向扩大器件的间隔,从而避免违反某些设计规则。

之前所有的方法都遇到了相同的问题。它们从未真正顾及到模拟,而是过于算法化,试图通过蛮力或随机概率复制人们所获得的解决方案。要获得“良好”的版图设计,需要工程师对问题进行高度约束。这是一项艰巨的任务,通常需要进行多次迭代才能为每个设计找到一组良好的约束条件。

此外,这些算法的核心不理解设计规则,CAD团队需要维护极其复杂的技术文件,这就包含所有规则。然后,产生的解决方案通常仍然包含大量违反设计规则的问题需要解决。总体而言,以前的方法对生产效率的影响充其量是微不足道的,而且常常不利。

经过这么多年失败的尝试,设计人员对模拟版图设计是否可以实现自动化表示怀疑,这也可以理解。许多人认为,这简直是个过于复杂的问题而永远无法解决。

模拟版图设计自动化工具的属性

那么,模拟版图设计自动化工具需要具备哪些属性,才能完成这项看似不可能的任务呢?

● 模拟电路识别:该工具必须要能了解和理解许多模拟电路结构,并能够在它们出现在所工作的电路中时识别它们。

● 自动约束:了解电路之后,该工具需要为其自身生成适当的约束条件,而无需工程师花费数小时来编辑它们。

● 模拟版图设计策略:该工具必须能在其算法中内置许多经过实践检验的版图设计策略,并将版图设计与电路理解和约束条件联系起来。

● 遵守深入的设计规则:算法核心的深处要能真正理解设计规则。该工具不仅要有检查错误的能力,而且还必须能在第一时间避免错误的形成。

● 灵活性:模拟设计工作是非常困难的,硬性规定的版图设计风格一旦被采用,即意味着失败。严格遵守约束条件会生成低质量的版图。一个成功的模拟自动化工具需要灵活的才智,以便在需要的地方达到良好的效果。

● 易于使用:模拟设计流程已经很复杂了,流程中的任何新工具都必须让工程师的任务更容易,而不是更难。

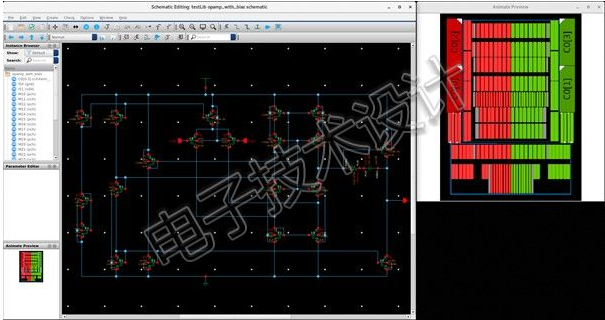

经过多年的研究和开发,Pulsic团队最近推出了一款新工具,称为Animate Preview,这款工具试图涵盖所有上述属性。Animate Preview集成到了电路工程师的原理图环境中(图3)。当工程师仍在编辑其原理图时,该工具会自动为电路创建一个版图视图,而为他们提供设计决策方面的快速反馈。工程师可获取其电路详细版图的可视化数据以及准确的面积估算。

Pulsic把这些版图称为“预览”,它们是高质量的自动生成的电路版图视图。Pulsic并没有声称这些版图是终极品质,但它们已经非常接近了,比之前任何工具所生成的视图都要更接近终极品质。先前所讨论的、为电路生成约束条件的问题得到了解决。Animate可以理解模拟电路拓扑,并自动为电路生成适当的约束条件(当然,工程师也可自行编辑约束条件以达到特定结果)。Animate Preview的算法对设计规则有深刻的理解,并且其所生成的结果是满足DRC要求的,因此工程师就能充分信任这些版图预览。同样,布局是在考虑布线的情况下进行的,实际上,许多关键结构将在版图预览中进行布线。

Animate Preview背后的想法是消除电路工程师和版图设计师之间的诸多循环,从而帮助他们更快地完成设计,并提高生产效率。