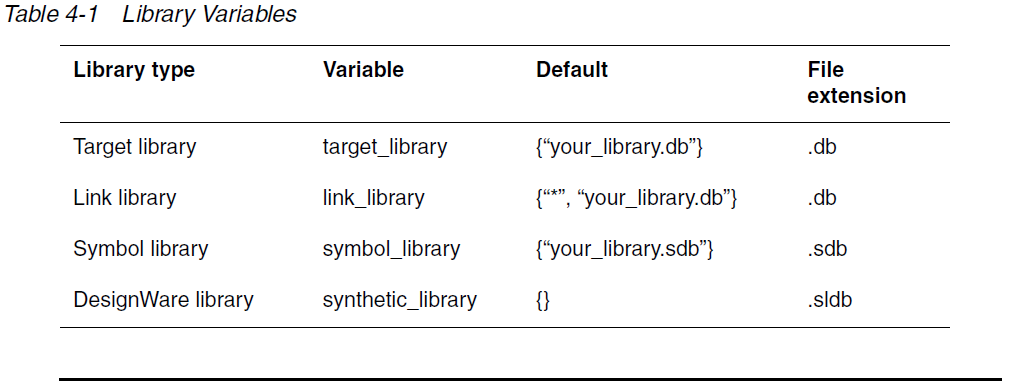

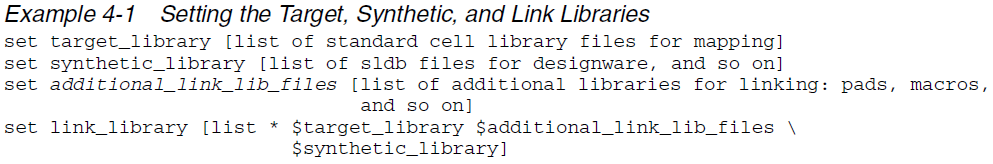

工艺库都是以.db为后缀的,它们在不同使用场景下有更为具体的称谓,一般有目标库和链接库的说法。目标库( target libraries )是DC在映射(编译、翻译)的过程中的使用的,包含产生网表和整个设计工作环境的必要信息。在DC中,目标库自动成为本地链接库( local_link_library )。除了本地链接库,还可以指定系统链接库( system link libraries (link_library variable))。链接库用来解析设计中需要参考的cell。

Technology Libraries

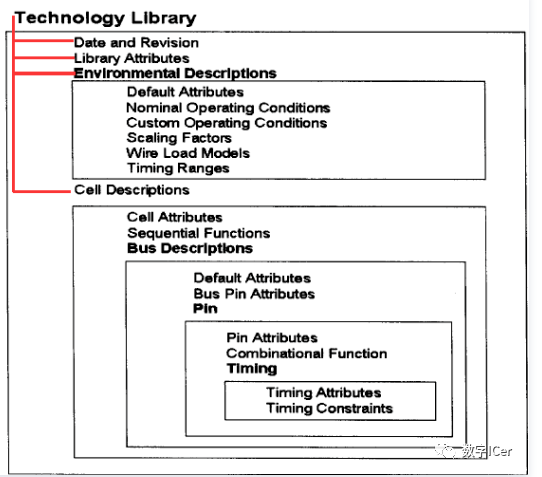

Technology libraries contain information about the characteristics and functions of each cell provided in a semiconductor vendor’s library. Semiconductor vendors maintain and distribute the technology libraries

Cell characteristics include information such as cell names, pin names, area, delay arcs, and pin loading. The technology library also defines the conditions that must be met for a functional design (for example, the maximum transition time for nets). These conditions are called design rule constraints.

In addition to cell information and design rule constraints, technology libraries specify the operating conditions and wire load models specific to that technology.

Design Compiler supports logic libraries that use nonlinear delay models (NLDMs), Composite Current Source (CCS) models (either compact or noncompact), or both NLDM and CCS models. The tool automatically selects the type of timing model to use based on the contents of the logic library. If a library contains both NLDM and CCS models, the tool uses the CCS models. During logic synthesis and preroute optimization, the tool might not use all the available CCS data to save runtime.

Design Compiler requires the technology libraries to be in .db format. In most cases, your semiconductor vendor provides you with .db formatted libraries. If you are provided with only library source code, see the Library Compiler documentation for information about generating technology libraries.

Design Compiler uses technology libraries for these purposes:

• Implementing the design function

The technology libraries that Design Compiler maps to during optimization are called target libraries. The target libraries contain the cells used to generate the netlist and definitions for the design's operating conditions.

The target libraries that are used to compile or translate a design become the local link libraries for the design. Design Compiler saves this information in the design's local_link_library attribute. For information about attributes, see “Working With Attributes” on page 5-40.

• Resolving cell references

The technology libraries that Design Compiler uses to resolve cell references are called link libraries.

In addition to technology libraries, link libraries can also include design files. The link libraries contain the descriptions of cells (library cells as well as subdesigns) in a mapped netlist.

Link libraries include both local link libraries (local_link_library attribute) and system link libraries (link_library variable).

For more information about resolving references, see “Linking Designs” on page 5-13.

• Calculating timing values and path delays

The link libraries define the delay models that are used to calculate timing values and path delays. For information about the various delay models, see the Library Compiler documentation.

• Calculating power consumed

For information about calculating power consumption, see the Power Compiler User Guide.